Proyecto Fin de Grado Grado en Ingeniería de las Tecnologías Industriales

Diseño y desarrollo del BMS de un monoplaza de Formula Student Electric

Autor: Germán Emilio Macías Gago

Tutor: Alfredo Pérez Vega-Leal

Departamento de Ingeniería Electrónica Escuela Técnica Superior de Ingeniería Universidad de Sevilla

Sevilla, 2017

## Proyecto Fin de Grado Grado en Ingeniería de las Tecnologías Industriales

# Diseño y desarrollo del BMS de un monoplaza de Formula Student Electric

Autor:

Germán Emilio Macías Gago

Tutor:

Alfredo Pérez Vega-Leal Profesor contratado doctor

Departamento de Ingeniería Electrónica Escuela Técnica Superior de Ingeniería Universidad de Sevilla Sevilla, 2017

| Proyecto de Fin d | de Grado: Diseño y desarrollo del BMS de un monopla    | nza de Formula Student Electric |

|-------------------|--------------------------------------------------------|---------------------------------|

|                   |                                                        |                                 |

|                   |                                                        |                                 |

| Autor:            | Germán Emilio Macías Gago                              |                                 |

| Tutor:            | Alfredo Pérez Vega-Leal                                |                                 |

|                   |                                                        |                                 |

| El tribunal nomb  | rado para juzgar el Proyecto arriba indicado, compuest | to por los siguientes miembros: |

| Presidente:       |                                                        |                                 |

|                   |                                                        |                                 |

| Vocales:          |                                                        |                                 |

|                   |                                                        |                                 |

|                   |                                                        |                                 |

| Secretario:       |                                                        |                                 |

|                   |                                                        |                                 |

| Acuerdan otorga   | rle la calificación de:                                |                                 |

| Ticuciani otorgan | The la camicación de.                                  |                                 |

|                   |                                                        |                                 |

|                   |                                                        |                                 |

|                   |                                                        |                                 |

|                   | El                                                     | Secretario del Tribunal         |

|                   |                                                        |                                 |

|                   |                                                        |                                 |

|                   | Fe                                                     | echa:                           |

# **Agradecimientos**

A mi familia, y en especial a mi madre María Dolores, quienes me han dado los valores de trabajo, dedicación y esfuerzo que hoy me hacen ser la persona que soy y me lo han facilitado todo para llegar hasta aquí, con inconmensurable paciencia y cariño.

A mi tutor Alfredo, por ofrecerme la oportunidad de trabajar junto a él en este proyecto, por dedicarme su tiempo y su constante atención.

# Resumen

La Formula SAE o Formula Student es una competición a nivel universitario en la que 600 universidades de todo el mundo diseñan, desarrollan y construyen monoplazas de carreras para superar una serie de pruebas. Este documento recoge el desarrollo y prototipado del Battery Management System de la batería del futuro ART18e, el primer monoplaza eléctrico del equipo ARUS.

Pese a la existencia de soluciones comerciales que cumplen los requisitos establecidos por la competición, su elevado costo y el afán de aprendizaje de nuevas tecnologías existente en el equipo son motivos suficientes para optar por el desarrollo propio en los laboratorios de la Universidad de Sevilla.

El proyecto trata de la forma más estructurada posible los subsistemas y funciones que comprenden este BMS, tales como monitorización de voltaje, temperatura, corriente y balanceo, ajustándose a los requisitos exigidos por el monoplaza y la normativa de FSAEE.

Partiendo desde una breve introducción de las tecnologías que envuelven a las celdas de ion litio y su caracterización se llega a la fabricación de cada PCB que conforma el proyecto, pasando por la definición de la topología, la elección de cada componente, el diseño de cada parte y el desarrollo hardware que lo acompaña, sin olvidar la interfaz de comunicaciones seguida con cada uno de los numerosos elementos.

Se recoge aquí la materialización de muchos meses de trabajo y estudio de tecnologías completamente nuevas para mí y para el equipo, y sienta el precedente de la que a partir de ahora será una tradición en ARUS.

# **Abstract**

Formula SAE, also known as Formula Student is a student engineering competition in which 600 universities around the world design, develop and build a formula style racing car to overcome a series of tests. This document gather the development and prototyping phase of the Battery Management System of the future ART18e, the first electric car of the ARUS team.

Although commercial solutions which satisfies the requirements of the competition can be found, its elevated cost and the knowledge persecution of the team are reasons enough to choose the self-development option in the laboratories of the University of Seville.

This project describes the subsystems and functions of this BMS, like voltage monitoring, temperature monitoring, current monitoring and cell balancing adjusting to the car topology and FSAEE rules requirements.

Starting of a brief introducction to the lithium ion cells and his characteristics, we reach to each PCB manufacturing covered in this project, passing by the topology definition, each component choice, each subsystem desing and the hardware developmente attached to it, without forgetting the communication interface of each element.

Many months of work are here reflected while completelly unknown technologies for me and the team have been studied, so this project should set a precedent and a new tradition of the team, the self developed BMS.

# Índice

| Agradecimientos                                                                                                                                                                                                                                                                   |                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Resumen                                                                                                                                                                                                                                                                           | III                                        |

| Abstract                                                                                                                                                                                                                                                                          | V                                          |

| Índice                                                                                                                                                                                                                                                                            | VII                                        |

| Índice de Tablas                                                                                                                                                                                                                                                                  | IX                                         |

| Índice de Figuras                                                                                                                                                                                                                                                                 | X                                          |

| Notación                                                                                                                                                                                                                                                                          | XIII                                       |

| <ul><li>1 Introducción</li><li>1.1. Motivaciones</li><li>1.2. Alcance del Proyecto</li><li>1.3. Topología del sistema</li></ul>                                                                                                                                                   | 1<br>1<br>1<br>2                           |

| 2 Celdas de ion-litio 2.1. Contexto tecnológico 2.1.1. Temperatura 2.1.2. Voltaje 2.1.3. Encapsulado 2.1.4. Energía 2.1.5. Proceso de carga 2.2. Especificaciones                                                                                                                 | <b>4</b> 4 5 6 6 7                         |

| 3 Gestión de baterías 3.1. Monitorización de baterías 3.1.1. Criterios de diseño 3.1.2. Monitorización de voltaje 3.1.3. Monitorización de temperatura 3.1.4. Monitorización de corriente 3.2. Balanceo 3.2.1. Introducción 3.2.2. Criterio de diseño 3.2.3. Circuito de balanceo | 9<br>9<br>10<br>12<br>14<br>15<br>15<br>17 |

| 4 Desarrollo hardware 4.1. Módulo esclavo 4.1.1. Circuito de alimentación 4.1.2. Subsistema de Balanceo 4.1.3. Microcontrolador                                                                                                                                                   | <b>21</b><br>21<br>22<br>23<br>24          |

| 4.1.4. Subsistema de temperatura                | 26        |

|-------------------------------------------------|-----------|

| 4.1.5. Subsistema de voltaje                    | 27        |

| 4.2. Módulo del Maestro                         | 28        |

| 4.2.1. Subsistema de intensidad                 | 29        |

| 4.2.2. Aislamiento galvánico                    | 29        |

| 4.2.3. Circuito de alimentación                 | 31        |

| 4.2.4. Subsistema de comunicación CAN           | 32        |

| 4.2.5. Microcontrolador y comunicación SPI      | 33        |

| 5 Comunicaciones                                | 35        |

| 5.1. Introducción al protocolo SPI              | 35        |

| 5.1.1. Lógica tri-estado                        | 37        |

| 5.2. Comunicación con dispositivos              | 37        |

| 5.2.1. Comunicación con AD7490                  | 37        |

| 5.2.2. Comunicación con MAX7317                 | 41        |

| 5.2.3. Comunicación con AD7988-5                | 43        |

| 5.3. Comunicación entre μCs                     | 44        |

| 5.3.1. Código de la comunicación                | 44        |

| 5.3.2. Codificación                             | 46        |

| 6 Fabricación                                   | 48        |

| 6.1. Fabricación de PCBs                        | 48        |

| 6.2. Batería de pruebas                         | 51        |

| 7 Evolución de prototipos                       | 52        |

| 7.1 Primer prototipo de 8 celdas                | 52        |

| 7.2. Segundo prototipo de 8 celdas              | 53        |

| 7.3. Módulo de corriente y temperatura          | 54        |

| 7.4. Prototipo final de 16 celdas               | 55        |

|                                                 |           |

| 8 Código                                        | <b>56</b> |

| 8.1. Code Composer Studio                       | 56<br>57  |

| 8.2. Código del Slave<br>8.3. Código del Master | 65        |

| •                                               |           |

| 9 Conclusión                                    | 78        |

| 9.1. Líneas futuras del sistema                 | 78        |

| 9.2. Presupuesto                                | 79        |

| 10 Documentos                                   | 81        |

| 10.1 Layout PCB                                 | 81        |

| 10.2 Normativa FSAEE                            | 83        |

| Referencias                                     | 86        |

|                                                 |           |

# ÍNDICE DE TABLAS

| Tabla 3–1. Resumen de especificaciones                            | 9  |

|-------------------------------------------------------------------|----|

| Tabla 5–1. Estructura del registro de control del AD7490          | 37 |

| Tabla 5-2. Función de los bits del registro de control del AD7490 | 38 |

| Tabla 5-3. Configuración del modo de operación del AD7490         | 38 |

| Tabla 5-4. Configuración del registro de control del AD7490       | 40 |

| Tabla 5-5. Configuracion del byte de comando del MAX7317          | 41 |

| Tabla 5-6. Formato de los registros de salida del MAX7317         | 42 |

| Tabla 9-1. Desglose de precios de los componentes                 | 81 |

# ÍNDICE DE FIGURAS

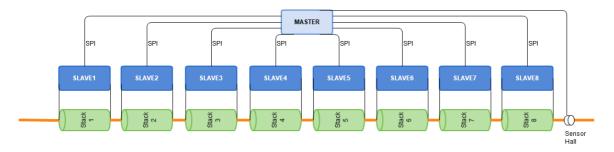

| Figura 1-1. Topología del BMS.                                     | 3  |

|--------------------------------------------------------------------|----|

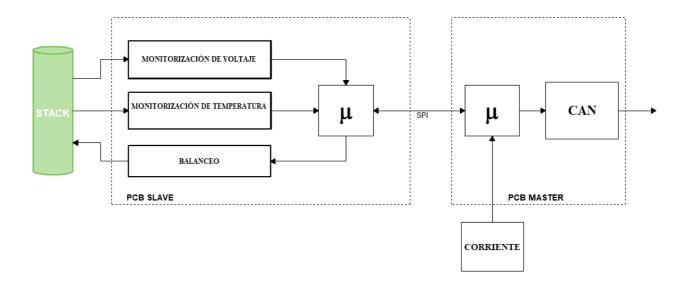

| Figura 1-2. Diagrama de bloques de las PCBs.                       | 3  |

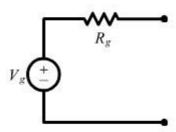

| Figura 2-1. Modelo de una celda                                    | 4  |

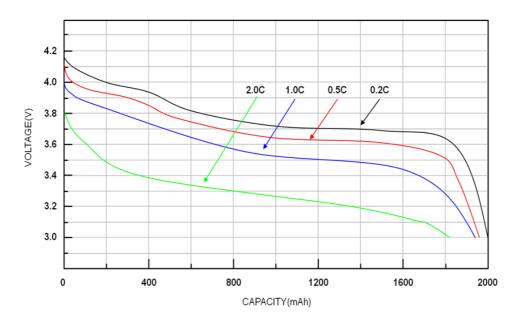

| Figura 2-2. Curvas de descarga de una celda de ion-litio           | 5  |

| Figura 2-3. Encapsulado Pouch, Cilíndrico y Prismático             | 6  |

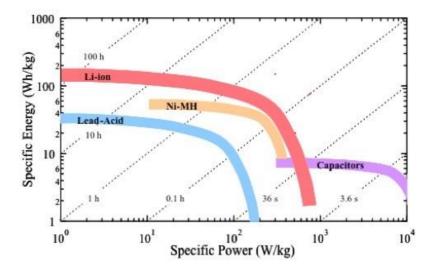

| Figura 2-4. Diagrama de Ragone                                     | 7  |

| Figura 2-5. Ejemplo del proceso de carga de una celda de ion-litio | 8  |

| Figura 2-6. Modelo 3D de un módulo 6p                              | 8  |

| Figura 3-1. Esquema de monitorización de voltaje                   | 10 |

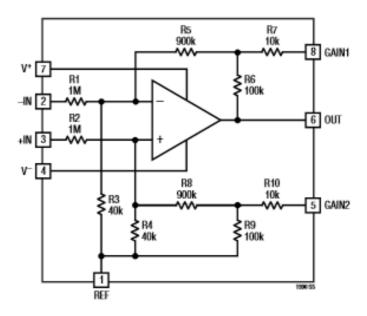

| Figura 3-2. Diagrama interno LT1990                                | 11 |

| Figura 3-3. Pinout LT1990                                          | 12 |

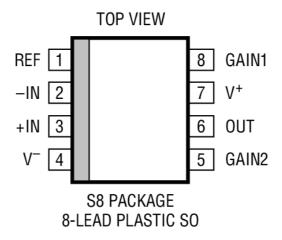

| Figura 3-4. Diagrama de bloques de LMT87                           | 13 |

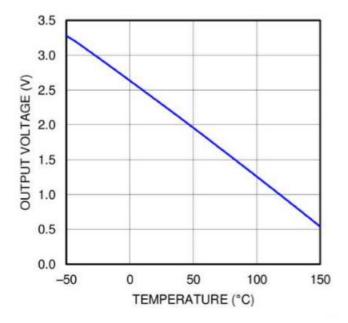

| Figura 3-5. Relación de voltaje de salida y temperatura            | 13 |

| Figura 3-6. Esquema de funcionamiento del sensor LEM               | 14 |

| Figura 3-7. Pack de baterías con balanceo y sin balanceo           | 16 |

| Figura 3-8. Ejemplo de proceso de balanceo                         | 17 |

| Figura 3-9. Circuito de balanceo                                   | 18 |

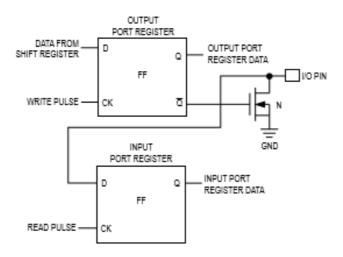

| Figura 3-10. Puerto del expansor de E/S                            | 19 |

| Figura 3-11. Esquema completo del circuito de balanceo             | 20 |

| Figura 4-1. Subsistemas PCB Slave                                  | 21 |

| Figura 4-2. Diagrama de conexión típica del AD1582                 | 22 |

| Figura 4-3. Diagrama de configuración del ADR130                   | 22 |

| Figura 4-4. Diagrama de funcionamiento básico del LM1117           | 23 |

| Figura 4-5. Esquema interno TLP293-4                               | 23 |

| Figura 4-6. Esquema interno MAX7317                                | 24 |

| Figura 4-7. Esquemático del subsistema del MSP430G2553             | 25 |

| Figura 4-8. Esquema de funcionamiento AD7490                       | 26 |

| Figura 4-9. Esquemático del subsistema de temperatura              | 27 |

| Figura 4-10. Esquemático del subsistema de voltaje                 | 28 |

| Figura 4-11. Subsistemas PCB Master                                | 28 |

| Figura 4-12. Esquemático subsitema de intensidad                   | 29 |

| Figura 4-13 Senaración de los planos de alimentación               | 30 |

| Figura 4-14. Esquemático ISO7241C                             | 31 |

|---------------------------------------------------------------|----|

| Figura 4-15. Esquemático del circuito de alimentación         | 31 |

| Figura 4-15. Diagrama de conexión típica del LM7805           | 32 |

| Figura 4-17. Esquemático del subsistema CAN                   | 33 |

| Figura 4-18. Esquemático del Microcontrolador                 | 34 |

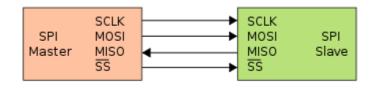

| Figura 5-1. Ejemplo de SPI con un Maestro y un Esclavo        | 35 |

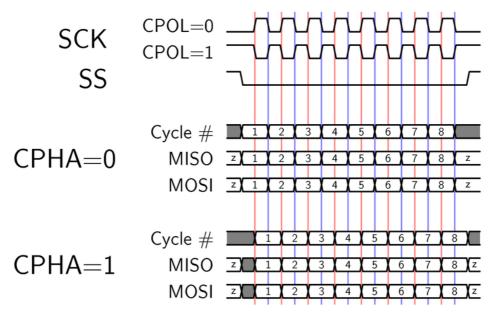

| Figura 5-2. Configuración de polaridad y fase del reloj       | 36 |

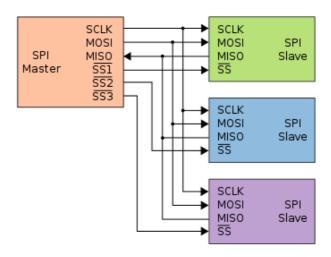

| Figura 5-3. Ejemplo de SPI con un Maestro y varios Esclavos   | 36 |

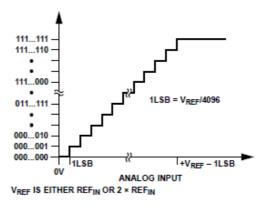

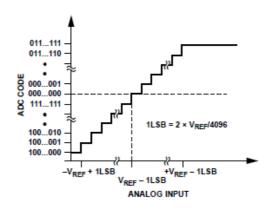

| Figura 5-4. Codificación Straight Binary                      | 39 |

| Figura 5-5. Codificación en dos complementos                  | 39 |

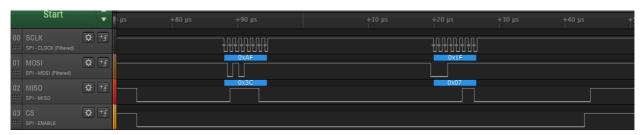

| Figura 5-6. Ejemplo de transmisión completa con AD7490        | 40 |

| Figura 5-7. Detalle de un fragmento de transmisión con AD7490 | 40 |

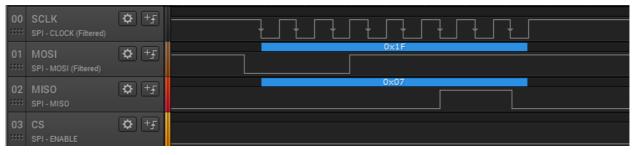

| Figura 5-8. Ejemplo de transmisión con el MAX7317             | 42 |

| Figura 5-9. Configuración de la comunicación del AD7988       | 43 |

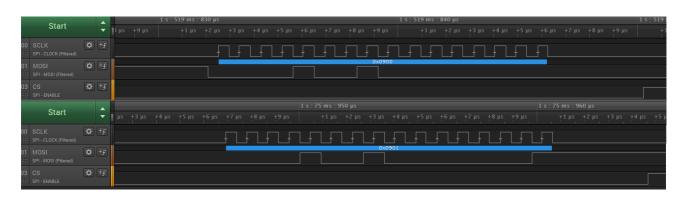

| Figura 5-10. Codificación de la comunicación entre μCs        | 47 |

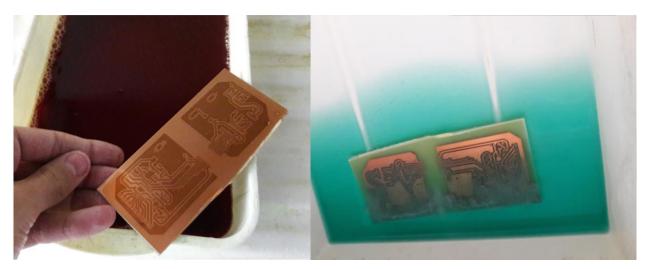

| Figura 6-1. Caras de la PCB impresas en papel vegetal         | 48 |

| Figura 6-2. Placa virgen recortada                            | 49 |

| Figura 6-3. Insoladora en funcionamiento                      | 49 |

| Figura 6-4. PCB durante el proceso de revelado y quemado      | 50 |

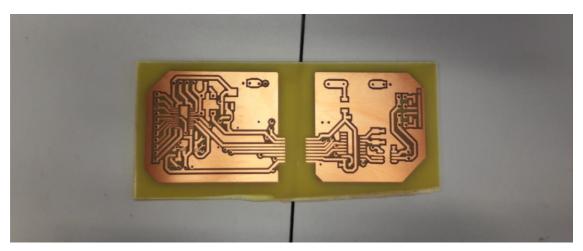

| Figura 6-5. Acabado final de la PCB                           | 51 |

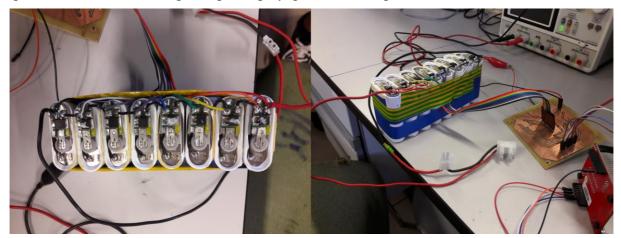

| Figura 6-6. Batería de pruebas                                | 52 |

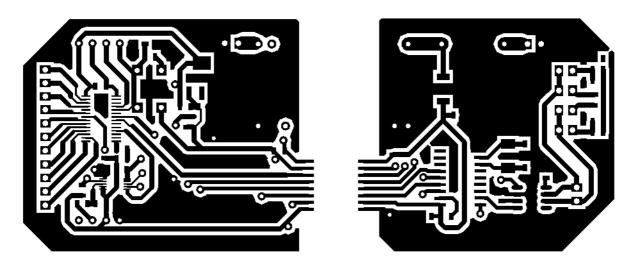

| Figura 7-1. Primer prototipo de BMS                           | 53 |

| Figura 7-2. Segundo prototipo de BMS                          | 55 |

| Figura 7-3. Módulo de corriente y temperatura                 | 56 |

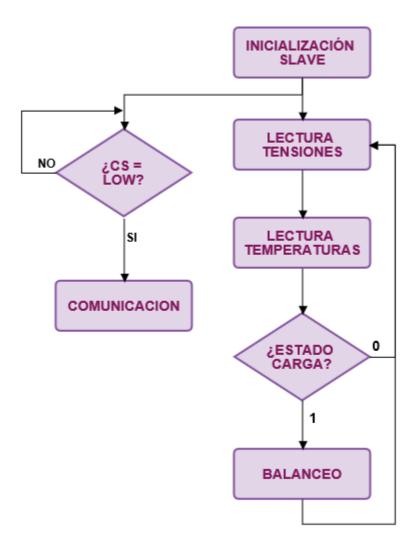

| Figura 8-1. Entorno CCS Edit View                             | 57 |

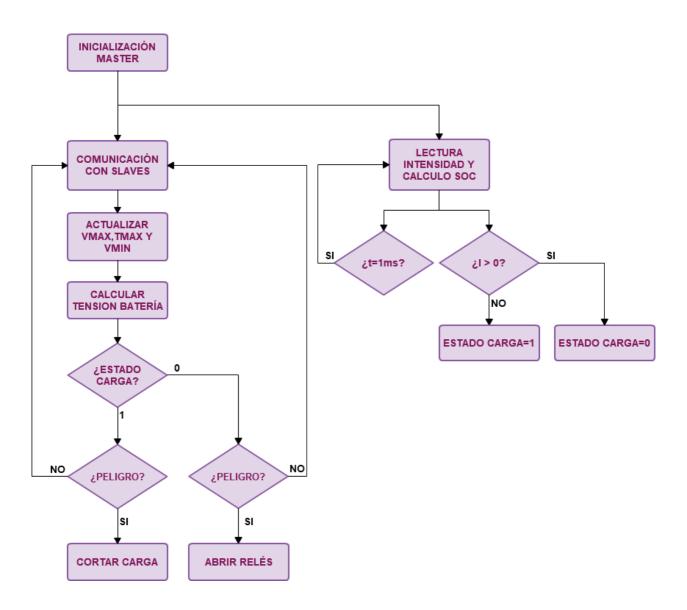

| Figura 8-2. Diagrama de flujo del código del Slave            | 58 |

| Figura 8-3. Diagrama de flujo del código del Master           | 66 |

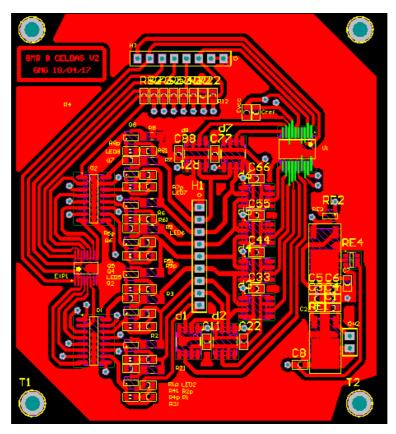

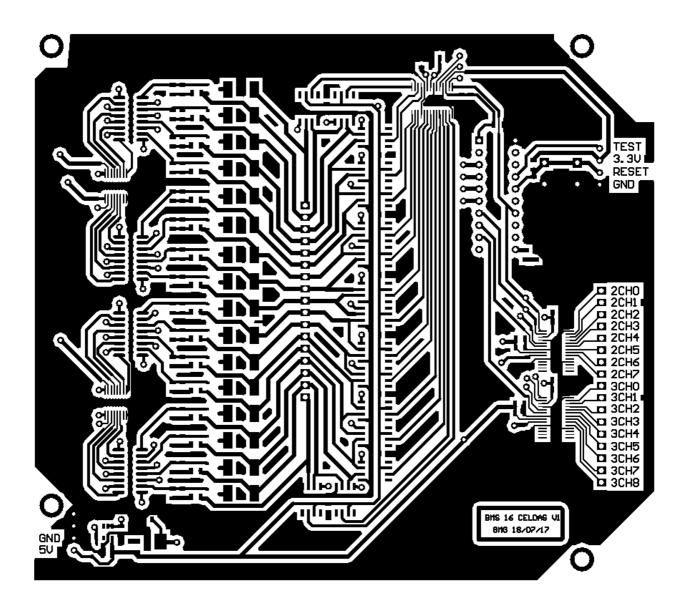

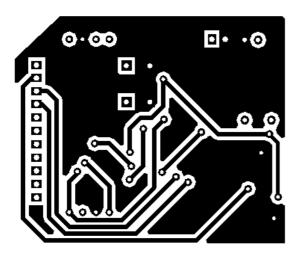

| Figura 10-1. Cara superior del Slave                          | 82 |

| Figura 10-2. Cara inferior del Slave                          | 83 |

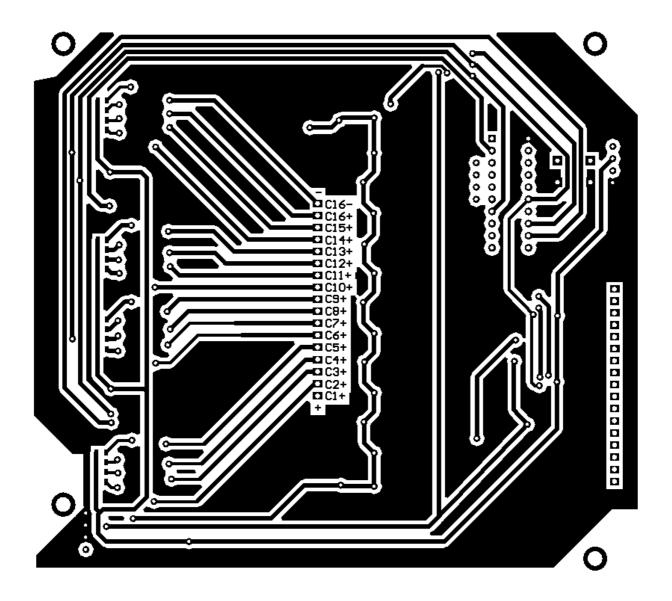

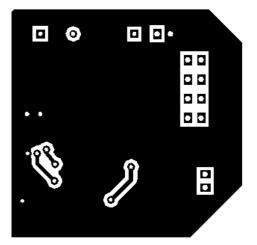

| Figura 10-3. Cara superior del Master                         | 84 |

| Figura 10-4. Cara inferior del Master                         | 84 |

# Notación

AD **Amplificador Diferencial ADC** Convertidor analógico-digital

AIR Relé electromagnético de aislamiento

**BMS** Sistema de gestión de baterías **CAN** Controller Area Network **CCS** Code Composer Studio

CS Chip Select

**EMI** Interferencia electromagnética

**FSAE** Formula Student

Formula Student Electric **FSAEE** Alto Voltaje >60VDC HV IC Circuito Integrado **LED** Diodo Emisor de Luz LV Bajo Voltaje <60VDC **MISO** Master Imput Slave Output **MOSI** Master Output Slave Imput **PCB**

**PTC** Posistor **SCLK** Señal de reloj SOC Estado de carga

SPE Sistema de Propulsión Eléctrica SPI Serial Peripheral Interface

**UART** Transmisor-Receptor Asíncrono Universal

Placa de circuito impreso

Microcontrolador μC

# 1 Introducción

Electrica han provocado un grandísimo desarrollo de las tecnologías electrónicas en el ámbito del automovilismo, consolidando el desarrollo del Sistema de Propulsión Eléctrica como el eje central del área. Tanto es así, que han nacido dos categorías oficiales de competición con monoplazas tipo Formula centradas principalmente en el desarrollo del SPE, la Formula E y la Formula Student Electric.

El BMS, o Battery Management System, es una parte fundamental en el Sistema de Propulsión Eléctrica de un coche, debe asegurar la correcta gestión de la energía contenida en la batería hacia el resto del vehículo, no dejando en ningún momento que la batería opere en un rango de funcionamiento inseguro.

Aunque el desarrollo del BMS sea algo anterior a la llegada del vehículo eléctrico, el problema a resolver en el interior de un monoplaza de competición cambia por completo las especificaciones de lo conocido hasta ahora y exige partir casi desde cero en la resolución del problema.

En este proyecto se va a proceder al diseño desde cero de un BMS para la batería del futuro monoplaza del equipo ARUS de la Universidad de Sevilla.

## 1.1 Motivaciones

La construcción de un monoplaza eléctrico es gran reto tecnológico a manos de la Ingeniería Eléctrica y Electrónica, y dado el interés por parte del equipo ARUS en participar en la Formula Student Electric y el gran desarrollo en tecnologías eléctricas existente en la propia Universidad de Sevilla, se tomó la decisión de desarrollar propiamente el máximo de sistemas posibles del vehículo, sin otro objetivo mas que la adquisición de conocimientos de los miembros y profesores implicados y el aprendizaje de nuevas tecnologías relacionadas con el automovilismo. Así pues, dado el elevado coste de las soluciones comerciales válidas para la batería del monoplaza, se optó desde un comienzo por el diseño propio del BMS, otorgándonos un infinito conocimiento sobre nuestro propio sistema, una mayor versatilidad y un menor coste.

El desarrollo de un proyecto de esta magnitud me ha otorgado un inmenso conocimiento práctico que no ha sido posible adquirir mediante el grado, que complementa a la perfección mi formación como futuro ingeniero.

## 1.2 Alcance del Proyecto

El BMS desarrollado en este proyecto trata de cumplir las especificaciones exigidas por la FSAEE adaptado a la topología del coche. No contiene en sí mismo las mismas especificaciones del BMS de una batería cualquiera.

El aquí propuesto cuenta con:

- Medición de voltaje de cada celda

- Medición de temperatura de las celdas

- Medición de corriente de salida o entrada a la batería

2 Introducción

- Balanceo pasivo

- Estimación del SOC

- Capacidad de comunicación CAN con el resto del vehículo

- Aislamiento eléctrico respecto al sistema de LV del vehículo

Así mismo, y como contempla la normativa de FSAEE, el BMS debe ser el encargado de transmitir la orden de permitir el flujo de corriente de la batería a la gestión de potencia del vehículo en caso de situación peligrosa para la misma, el poder de corte recae en unos relés electromecánicos que no forman parte del BMS.

El objetivo de este proyecto ha sido el desarrollo de una base hardware y unas funciones mínimas del BMS exigidas por la normativa de FSAEE, con opciones a seguir un desarrollo software más completo y con más funcionalidades durante el restante año de evolución.

## 1.3 Topología del sistema

Existen diferentes formas de disponer los circuitos de medida, descarga y procesado necesarios para implementar un sistema de gestión de baterías, pero básicamente pueden clasificarse en tres las topologías de un BMS: centralizado, modular y distribuido.

En un BMS centralizado todos los circuitos pertenecen a la misma PCB, de la que salen los cables a cada celda, requiere de una gran PCB si el tamaño de la batería es considerable y es la peor opción en términos de organización del cableado.

Un BMS modular es similar en concepto a un BMS centralizado, pero subdivido en distintos módulos más pequeños, que permiten una mejor organización. Puede tener una jerarquía *Master-Slave* o los módulos pueden ser independientes entre sí.

En un BMS distribuido cada celda tiene su propia PCB para la medida de voltaje y temperatura, con su circuito de balanceo y comunicaciones. Es la topología más eficiente en organización y cableado, pero eleva el coste y la complejidad sea cual sea el número de celdas.

La topología elegida es la de BMS modular, es decir, un *Master* central que gobierna a 8 *Slaves* o módulos. Cada uno de estos módulos está asociado a cada uno de los segmentos o *stacks* de la batería.

Cada *stack* está compuesto por 16 celdas de ion-litio en serie, por lo que obviamente cada BMS *Slave* debe tener dicha capacidad. El conjunto de la batería está considerado por los 8 *stacks* en serie, con un total de 128 celdas en serie.

Figura 1-1. Topología del BMS

El BMS *Master* recopila la información de cada *Slave* y tiene un conocimiento general de toda la batería, así como la temperatura y tensión de cada celda. La comunicación entre *Master* y *Slaves* se realiza por SPI, que se explicará de una forma más detalla en el apartado 5 de comunicaciones. Como se puede observar, la detección de corriente es también tarea del *Master*, con un sensor de efecto Hall en el terminal negativo de la batería. El siguiente diagrama de bloques de la imagen recoge las funciones y su distribución en cada PCB.

Figura 1-2. Diagrama de bloques de las PCBs

# 2 CELDAS DE ION-LITIO

Ara entender la necesidad de un BMS en una batería es necesario conocer el carácter sensible de las celdas de ion-litio y las consecuencias que tiene llevar las celdas a sus respectivos límites. En este apartado se explicará brevemente lo más importante para entender el comportamiento de una celda de ion-litio y los parámetros con los que puede quedar caracterizada.

## 2.1 Contexto tecnológico

Una batería de ion-litio es un tipo de batería recargable en la que los iones de litio se desplazan desde el electrodo negativo al electrodo positivo durante la descarga, y vuelven durante la carga.

Las celdas de ion-litio poseen una serie de propiedas tales como alta densidad energética, ligereza en sus componentes, alta tasa de descarga, mínimo efecto memoria y alto rendimiento. Sin embargo, su rápida degradación y sensibilidad a las elevadas temperaturas, pueden resultar en su destrucción por inflamación o incluso explosión.

Estas celdas pueden ser sencillamente modeladas como una fuente de tensión real, es decir, una fuente de tensión ideal en serie con una resistencia interna, que suele ser del orden de varios  $m\Omega$ .

FIgura 2-1. Modelo de una celda

### 2.1.1 Temperatura

Una celda de ion-litio requiere operar en un rango de temperatura preciso, comúnmente recomendado por los fabricantes entre 0°C y 60°C. El mayor problema para operar en tal rango es el sobrecalentamiento producido por las mismas celdas durante su propio uso, dado que cuanta más carga se le exige a las mismas, mayor corriente pasa por la resistencia interna de la celda, que se traduce en mayor calor según la expresión del efecto Joule.

$$Q = I^2 \cdot R \cdot t$$

Donde Q es el calor, I la intensidad que circula por la celda, R su resistencia interna, y t el tiempo.

Los efectos de la temperatura en una celda pueden ser variados, desde una pequeña pérdida de rendimiento y capacidad, hasta una cadena de reacciones químicas incontrolables en el interior que producen una acumulación de gases provocando la ignición y a la explosion de la propia celda, poniendo en serio peligro el resto del conjunto si conviven más de una.

Por lo tanto, el BMS debe estar monitorizando continuamente la temperatura de las celdas críticas y mandar una señal en caso de ser necesario al circuito de refrigeración de la batería. Si la temperatura de cualquier celda excede los 57 grados centígrados, se mandará una señal al circuito de gestión de potencia que permitirá abrir los relés de seguridad, previo aviso al piloto.

### 2.1.2 Voltaje

La tension que proporciona una celda de ion-litio está caracterizada por tres valores; tension máxima (Vmax), tensión mínima (Vmin) y tensión nominal (Vnom). Al contrario que las fuentes de tensión ideales, la tensión de una celda es variable según su SOC, asímismo, también lo es según la intensidad que se extraiga de la misma, lo que significa que su tensión en circuito abierto no coincide con la tension sometida a una carga, debido a la caida de tensión que se experimenta en la resistencia interna. En la siguiente imagen se puede observar de una forma detallada (aunque algo exagerado) dicho comportamiento ante una intensidad constante de descarga.

Figura 2-2. Curvas de descarga de una celda de ion-litio

Matizar que C es la unidad que se utiliza para medir la carga o descarga de una celda, significando 1C la intensidad necesaria para descargar una celda en una hora, es decir, si una celda tiene 2300mAh de capacidad<sup>1</sup>, que descargue o cargue a 1C significa que la intensidad que cede o entra en la celda son 2300mA, si lo hace a 2C, la intensidad será de 4600mA.

Como se observa en la gráfica, las curvas de tensión tienen distinto comportamiento según la intensidad de descarga, cuanto menor sea la intensidad, más horizontal es la curva (más tiempo se mantiene la tensión cerca de Vnom), más capacidad se aprovecha de la batería, mejora el mantenimiento de la propia celda a la larga y más eficiente es la tranmisión de energía, disipando menos calor. Cuando la intensidad de descarga es mayor, aumenta la caida de tensión en la resistencia interna, quedando desaprovechada una parte de la tensión de la propia celda y alcanzando antes su tensión minima, lo que provoca una pérdida de la capacidad.

En la tensión máxima y minima de la celda reside la importancia del BMS. Una celda de ion-litio suele estar caracterizada entre 2.5V y 4.2V, siendo por seguridad no revasables ambos límites. Si una celda entra en lo que se conoce como *undervoltage* o *overvoltage* aumenta la temperatura de la misma exponencialmente perdiendo capacidades con daño permanente, y como se ha descrito anteriormente,

<sup>1</sup> Se define capacidad de una celda como el valor máximo de carga que puede almacenar. Se mide en amperios hora (Ah).

6 Celdas de ion-litio

un aumento excesivo de la temperatura puede producir inflamación e ignición en la celda. Es por eso por lo que el BMS debe evitar que la tensión de cualquier celda supere los 4.2V y disminuya de 2.5V, aunque en ocasiones por seguridad se deja un pequeño margen inferior que ayuda a alargar la vida de las celdas, como se observa en la Figura 2-2, se detiene la descarga a 3.0V.

#### 2.1.3 Encapsulado

El encapsulado de una celda es el empaquetado o el recubrimiento mecánico que la contiene. Las de ion-litio se fabrican por lo general en tres encapsulados diferentes: Semiflexible o Pouch, Cilíndrico y Prismático.

Figura 2-3. Encapsulado Pouch, Cilíndrico y Prismático

En las celdas tipo Pouch es común encontrarse la densidad energética más alta en comparación al resto, no disponen de recubrimiento metálico y son fácilmente perforables. Por otro lado, las celdas Cilíndricas suelen ofrecer una tasa de descarga muy alta con peor densidad salvo contados casos, además disponen de varios empaquetados estandarizados como 18650 o 26650 y las recubre una carcasa metálica. Las celdas prismáticas suelen ser algo pobres en densidad energética y en tasa de descarga, pero suelen tener capacidades muy altas. Son de mayor tamaño que las demás y tienen un recubrimiento más compacto y seguro.

Aunque las características de las celdas no tienen por qué depender de su empaquetado, esto es simplemente una convención seguida por muchos fabricantes.

#### 2.1.4 Energía

Despreciando el empaquetado de una celda, para un mismo tipo de reactivos la capacidad depende del volumen de los mismos, así pues, para dos celdas con la misma densidad energética, lógicamente una con mayor volumen tendrá mayor capacidad.

La energía almacenada en una celda se mide en Wh y se calcula mediante el producto de la tension en circuito abierto de la misma por su capacidad en Ah. La densidad energética se obtiene del cociente entre su energía almacenada en Wh y el volumen que ocupa en  $m^3$ .

Los dispositivos de almacenamiento de energía eléctrica se enfrentan a un compromiso entre la máxima potencia extraíble (alta tasa de descarga) y la capacidad de los mismos. En el caso de elegir una celda de alta capacidad, la máxima corriente extraíble de esa celda sería baja y viceversa. Dicho compromiso se muestra en el diagrama de Ragone.

Figura 2-4. Diagrama de Ragone

En las tecnologías de vehículos eléctricos y gracias a las propiedades del ion-litio, la elección de celdas se produce para que se cumplan al máximo los dos requisitos, eligiéndose comúnmente las celdas comprendidas en la esquina de la curva roja.

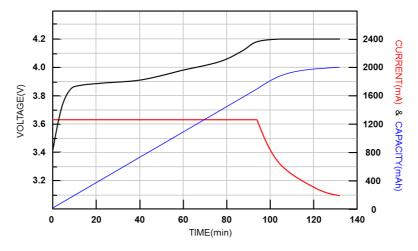

#### 2.1.5 Proceso de carga

La carga de una celda de ion-litio se realiza en dos etapas. En la primera etapa, el cargador de la batería proporciona una intensidad constante, mientras la tensión en los terminales va aumentando conforme aumenta la carga. Esta etapa concluye cuando se alcanza el valor máximo de tensión. Si la intensidad de la carga es mayor, el proceso es más rápido, pero más ineficiente (mayor disipación en la Rin y mayor temperatura). La tensión máxima de las celdas se ha alcanzado al finalizar esta etapa debido a la caída de tensión en la resistencia interna, sin embargo, las tensiones en circuito abierto no han llegado a su valor máximo.

En la segunda etapa, el cargador mantiene la tensión del valor máximo permitido constante y disminiye la intensidad pausadamente, partiendo del valor dado en la primera etapa. Bajando la intensidad la caída de tensión de la resistencia disminuye, por lo que poco a poco nos aproximamos a la carga total de cada celda en circuito abierto. El proceso concluye cuando la intensidad baja un cierto umbral, debido a que la curva que describe es una exponencial negativa y el proceso podría tardar indefinidamente.

Figura 2-5. Ejemplo del proceso de carga de una celda de ion-litio

8 Celdas de ion-litio

## 2.2 Especificaciones

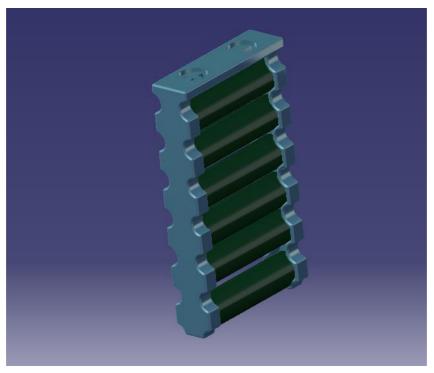

En nuestro caso, y en base al prediseño de la batería, las celdas usadas serán cilíndricas, concretamente del estándar 18650. Mediante la agrupación de grupos de 6 celdas en paralelo se consiguie la corriente de descarga y capacidad necesaria, y se disponen 128 de estas agrupaciones en serie para conseguir el voltaje necesario, comprendiendo un total de 768 celdas.

Las celdas elegidas en el prediseño son las Samsung 25R, con 2.5Ah de capacidad y casi 50A de intensidad máxima de descarga.

Para monitorizar los 128 módulos de 6p<sup>2</sup> celdas, se dividen en 8 stacks de 16 celdas en serie cada uno, como se ha especificado en el apartado 1.3. El BMS considera cada uno de los módulos de 6p como una única celda (al estar en paralelo todas comparten la misma tensión).

Dado que la competición obliga a monitorizar la temperatura de una de cada tres celdas como mínimo, se dispondrán dos sensores de temperatura por cada modulo 6p, monitorizando el conjunto de la segunda y tercera celda y el conjunto de la cuarta y quinta celda.

Figura 2-6. Modelo 3D de un módulo 6p

\_

$<sup>^2</sup>$  La nomenclatura usada en las configuraciones de baterías consiste en el número de celdas seguidas según su disposición. Por ejemplo, una batería con 10 celdas en serie y 5 en paralelo se nombra como 10s5p.

# 3 GESTIÓN DE BATERÍAS

A gestión de baterías conocida como *Battery Management* en inglés, se compone de dos partes, la monitorización y el balanceo. En este apartado se explicará detalladamente cómo se ha resuelto cada uno de estos problemas.

## 3.1 Monitorización de baterías

#### 3.1.1 Criterios de diseño

El objetivo del sistema de monitorización es satisfacer los requisitos de la FSAEE en términos de medida de voltaje y temperatura, como se desarrollará más adelante en los puntos 3.2.1 y 3.2.2. El voltaje debe ser monitorizado precisa y continuamente, lo que deja una interpretación bastante abierta. Por otro lado, en la temperatura especifica que la medida debe ser realizada en el terminal negativo de cada celda, o a no más de un centímetro del mismo, y que mínimo una de cada tres celdas debe ser monitorizadas. Se ha tomado como objetivo adicional la mayor semejanza posible con las soluciones comerciales comúnmente usadas por los equipos, teniendo una mayor flexibilidad al ser nuestro propio sistema.

Tabla 3–1. Resumen de especificaciones

| Especifiación                          | Objetivo                 |  |

|----------------------------------------|--------------------------|--|

| Rango de entrada de tensión por celda  | De 0V a 5V               |  |

| Precisión de medida de tensión         | 50mV                     |  |

| Tiempo de lectura de voltaje por celda | 200μs                    |  |

| Sensores de voltaje                    | 1 por celda              |  |

| Rango de medición de Temperatura       | 0°С а 70°С               |  |

| Sensores de Temperatura                | Hasta 2 de cada 3 celdas |  |

|                                        |                          |  |

La medida de la corriente entrante o saliente del conjunto de la batería es también otra parte del sistema de monitorización y aunque no estén impuestos sus criterios de diseño por la FSAEE, el objetivo a cumplir ha sido el que cubra el rango necesario de amperaje con cierto margen de seguridad, además de obviamente una alta precisión en la medida que nos permita una estimación de la potencia y del SOC de mayor calidad.

10 Gestión de baterías

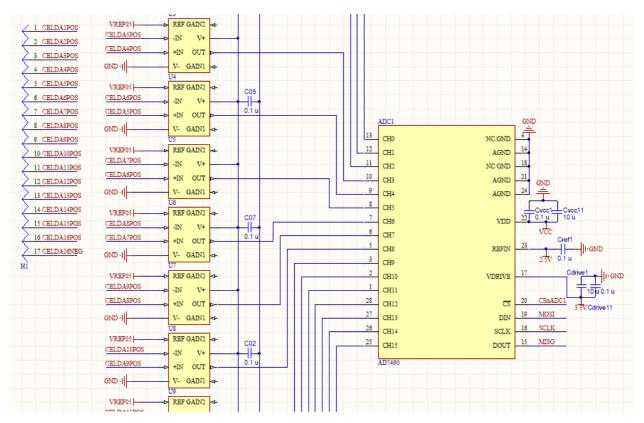

## 3.1.2 Monitorización de voltaje

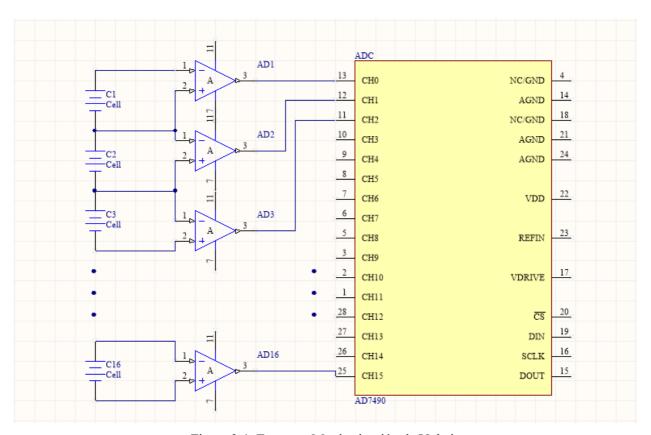

Figura 3-1. Esquema Monitorización de Voltaje

Para la medida en cada *Slave* de la tensión de cada una de las 16 celdas que hay en serie, se ha seguido el esquema de la imagen anterior. Pese a existir ICs que se encargan de la monitorización del voltaje de todas celdas, el número de celdas de entrada es fijo y menor a 16 en la mayoría de los casos, así que por versatilidad y por la aplicación de conocimientos adquiridos en Instrumentación Electrónica se ha optado por el uso de Amplificadores Diferenciales.

El modelo usado ha sido el LT1990A, que pese a no ser la opción de menor coste, proporciona gran precisión y fiabilidad, estando preparado para la monitorización de celdas y para aplicaciones de automoción.

El LT1990 o LT1990A (variante con mayor rechazo a modo común) tiene una impedancia de entrada de  $2M\Omega$  en modo diferencial, es decir, que la corriente del efecto de carga es totalmente despreciable. Permite un ancho rango de alimentación, de entre 2.7V y 36V incluyendo la posibilidad de alimentación simétrica, aunque no vaya a ser usada en nuestro caso. Ambos modelos proporcionan alto rechazo al modo común, 70db mínimo de CMRR.

Figura 3-2. Diagrama interno LT1990

La ganancia es configurable mediante los pines GAIN1 y GAIN2, si los pines permanecen desconectados obtendremos una ganancia G=1, si ambos se conectan a  $V_{REF}$  entonces G=10. En nuestro caso, y debido a que la alimentación que se le proporciona es de 5V y el rango de tensiones de medida estará entre 2.5V y 4.2V, evidentemente no tiene sentido escoger la ganancia G=10, por la saturación a 5V que se produciría en la salida.

La ecuación que gobierna la tensión de salida es la siguiente:

$$V_{OUT} = G \cdot (VIN^+ - VIN^-) + V_{REF}$$

El AD nos obliga a usar una referencia que no puede coincidir con  $V^-$ , es decir, no es posible el uso del rango de medición completo, porque Vref no puede ser 0V. Como se ve en la ecuación anterior, siendo Vout como máximo  $V^+$ , y tomando como ganancia G=1, si despejamos la entrada diferencial de tensión queda:

$$\Delta VIN = (VIN^+ - VIN^-) = Vout - Vref$$

Con lo cual todo lo que se aumente Vref se disminuye del rango de la tensión de entrada. Como se comentó en el apartado 2.1, la tensión de una celda de ion-litio oscila entre 4.2V y 2.5V, por lo que usando una referencia de 0.5V seríamos capaces de medir tensiones entre 0 y 4.5V. La razón del uso de Vref = 0.5V es experimental, puesto que el propio fabricante para el rango de alimentación usado recomienda Vref=1.25V [1], sin embargo, mediante la prueba en el laboratorio se ha comprobado que el resultado con la referencia elegida es igual de aceptable, permitiéndonos tener un rango válido de tensiones, aunque no se haya cumplido el objetivo inicial impuesto.

El encapsulado que nos proporciona Linear Technologies es SO-8, de reducido tamaño y sencillo de enrutar, con el pinout ilustrado en la siguiente figura.

Gestión de baterías

Figura 3-3. Pinout LT1990

Por último, las salidas de los AD se conenctan a un ADC de 16 canales (tal y como queda ejemplificado en la Figura 3-1) que transmitirá toda la información de las tensiones de cada celda en serie al microcontrolador para la monitorización.

Aunque se explicará en mayor detalle el funcionamiento del ADC AD7490 en los apartados de desarrollo hardware y código, aclarar que al tener una precisión de 12 bits y estar alimentado a 5V obtenemos una precisión de 1.22mV por LSB, y considerando todos los posibles errores contemplados en el datasheet, podemos obtener una precisión de alrededor de 10mV, mejor de lo contemplado en los objetivos iniciales.

## 3.1.3 Monitorización de temperatura

Partiendo de los requisitos de monitorización de temperatura antes mencionados, y dado que sólo existe un prediseño de la batería actual del coche, se ha tratado de realizar un sistema de medida lo más general posible, con capacidad para todas las alternativas barajadas hasta ahora.

Se consideraron incialmente diferentes opciones, entre ellas, el uso de PTCs y sus respectivos acondicionamientos, incluso se probó en el tercer prototipo (ver apartado 7 de evaluación de prototipos) el uso de una PT1000 con satisfactorios resultados. Pero a medida que se fue cerrando el prediseño de la batería, y al considerar la gran cantidad de celdas que llegarían a usarse y por ende la gran cantidad de sensores de temperatura, se optó por sensores comerciales preparados para aplicaciones de automoción, que proporcionaban una precisión similar a la PT1000 con mayor facilidad de implementación.

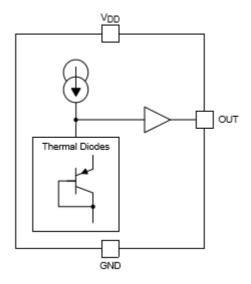

El modelo elegido es el LMT87LPG, es un modelo de sensor de temperatura CMOS con salida analógica lineal inversamente proporcional a la temperatura y precisión típica de 0.4°C. Su funcionamiento es tremendamente sencillo al solo disponer de 3 pines. Dos para su alimentación (que requiere de un condensador de 10nF entre ellos) y uno para la salida, como se observa en la figura proporcionada en la hoja del fabricante [2].

Figura 3-4. Diagrama de bloques de LMT87

El bajo consumo de cada sensor facilita la aplicación de un gran número de los mismos, y su rango de alimentación de ajusta al ya usado en los sistemas.

Como se ha mencionado anteriormente, el LMT87 ofrece una salida muy lineal en comparación con otras de las opciones consideradas, aunque Texas Instruments nos facilita una extensa tabla de valores, así como unas fórmulas de aproximación de la tabla, debido a que exite una pequeña forma parábolica apenas considerable en la gráfica.

Figura 3-5. Relación de voltaje de salida y temperatura

$$T = \frac{13.582 - \sqrt{(-13.582)^2 + 4 \cdot 0.00433 \cdot (2230.8 - V_{TEMP}(mV))}}{2 \cdot (-0.00433)} + 30$$

14 Gestión de baterías

Para obtener una aproximación más sencilla pero menos precisa válida para entre 0°C y 60°C también nos facilitan la siguiente expresión.

$$T = \frac{V(mV) - 2633}{-13.5667}$$

°C

En encapsulado elegido entre los posibles ha sido el TO-92S, necesariamente el through-hole para que fuese posible su montaje en la batería, y el 92S porque plantea el mejor comportamiento térmico de entre todos, con menor resistencia termal al ambiente y al empaquetado que el TO-92.

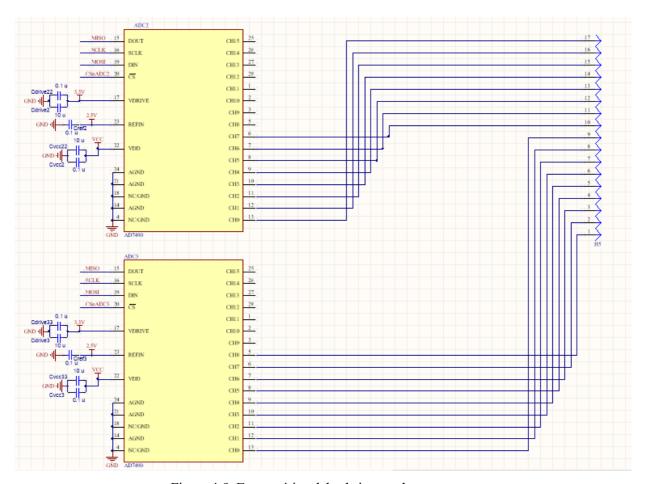

Por último, para que sea posible la lectura digital de las temperaturas por el microcontrolador del *Slave* se han usado dos ADC AD7490, el mismo modelo que el usado en la monitorización de voltaje. Aunque como se observa en el apartado del enrutado de las PCBs, pese a tener 16 canales cada uno, sólo se han usado 8. Esto es por lo comentado anteriormente de generalización, dado que en el prediseño de la batería se contemplan dos opciones, una de ellas requiere el doble de sensorización de temperatura que la otra, 32 sensores y 16 respectivamente. Por ello, si se necesitase finalmente de esas 32 entradas sólo habría que cambiar el enrutado y usar los 32 canales disponibles.

#### 3.1.4 Monitorización de corriente

La última función del sistema de monitorización es la de la medida de corriente, que se efectua mediante un sensor de efecto Hall. El principio de dicho sensor se basa en la medición la perturbación magnética creada por el paso de corriente, lo que no afecta en el consumo ni perturba la corriente que circula por la batería.

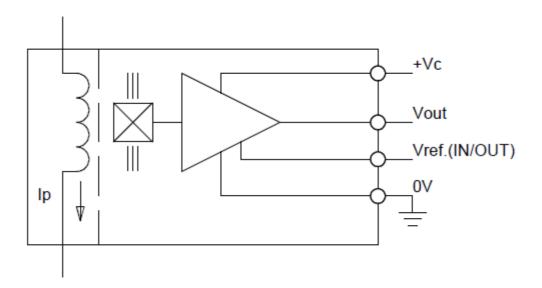

Figura 3-6. Esquema de funcionamiento del sensor LEM

En este caso, y dadas las altas corrientes que pueden salir o entrar en la batería, del orden de 250A, se ha elegido el sensor LEM HTFS 200-P, que además de tener gran facilidad de conexionado soporta hasta 300A.

Como se observa en la figura, tiene únicamente 4 pines, dos de los cuales son de alimentación, 5V y 0V. Se empleará como referencia 2.5V, lo que deja una gama partida de valores, la tensión de salida superará esa referencia cuando circule en el sentido de Ip especificado en la figura, y bajará de 2.5V cuando lo haga en el contario. La distribución de la salida es la siguiente:

$$V_{OUT} = V_{REF} \pm \left(1.25 \cdot \frac{I_P}{200}\right) V$$

En nuestro caso y para nuestro rango de intensidades la tensión de salida está acotada entre 4.0625V y 0.9375V, lo que deja un margen muy pequeño de tensión para el rango de corriente tan amplio que contemplamos. La forma de solventarlo es con un ADC capaz de medir a una altísima precisión, emplearemos el AD7988-5 de 16 bits alimentado a 5V, que nos otorga una precisión de LSB de 76.294  $\mu V$ , lo que se traduce en una precisión de medida de corriente de 12.2mA sin tener en cuenta los posibles errores del ADC. Más que suficiente para la aplicación que necesitamos. Los detalles del ADC se explicarán en el apartado de desarrollo hardware.

# 3.2 Balanceo

## 3.2.1 Introducción

El balanceo es una técnica utilizada durante la carga que permite maximizar la capacidad y aumentar la longevidad de un paquete de baterías con varias celdas.

Para aprovechar al máximo la capacidad hay que asegurarse que durante la carga todas las celdas tengan como mínimo un valor de carga igual al de la celda con menor capacidad, por lo tanto, si dicha celda llegase a cargarse por completo sin que las otras lo estén, habría que descargar parte de esa energía para poder cargarlas todas de nuevo, actuando la celda de menor capacidad como la limitante de todo el conjunto.

Dado que las baterías suelen estar formadas por el mismo tipo de celda, podría parecer a priori que el balanceo no es necesario, puesto que al tener las mismas propiedades se cargarían a la misma velocidad y hasta la misma capacidad. Nada más lejos de la realidad, cada celda, aunque igual en fabricación a las otras, tiene un comportamiento ligeramente distinto debido a su naturaleza química, por lo que el balanceo es una herramienta imprescindible en cualquier BMS.

Para ello existen dos métodos:

- Balanceo pasivo: La energía sobrante de la celda a balancear se elimina mediante un circuito resistivo, disipándose en forma de calor. Aunque es la forma menos eficiente de hacerlo, su facilidad de implementación y fiabilidad, además de bajo coste, lo hacen la opción más favorable para este proyecto.

- Balanceo activo: La energía sobrante de la celda a balancear se transfiere a otras celdas con menor carga, así mientras la celda con excesiva carga la disminiye, las celdas con menor carga la aumentan. Normalmente se realiza mediante convertidores DC/DC, lo que aumenta considerablemente el coste, además de la complejidad, siendo necesario un sistema de control del flujo energético.

Gestión de baterías

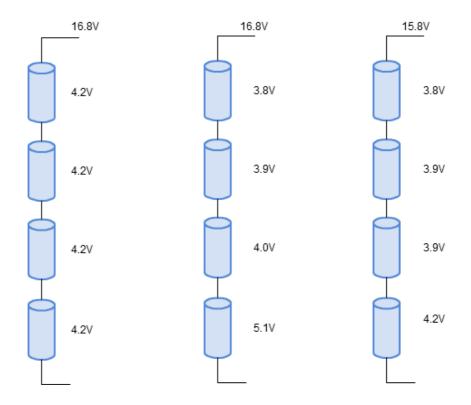

Figura 3-7. Pack de baterías con balanceo y sin balanceo

Como se observa en la imagen, la batería de la izquierda está completamente balanceada y se aprovecha el 100% de su capacidad. La batería del centro por otro lado, no tiene ningún tipo de balanceo y está aparentemente cargada a 16.8V, sin embargo, no posee un control del voltaje de cada celda y se han cargado independientemente poniendo a la batería en un estado peligroso. Por último, en la última batería se ha detenido la carga cuando una de las celdas ha llegado a su máxima capacidad, a pesar de ello, el resto no lo ha hecho y se ha desaprovechado una parte de la capacidad de la batería.

El proceso de balanceo se puede realizar de diversas formas; cuando alguna de las celdas supera en tensión a la celda con la tensión mínima, cuando alguna celda llegue al máximo, o también es común encontrarse que cada un cierto periodo se pare la carga y se igualen todas las tensiones, sin necesidad de haberse llegado al límite de tensión. El modo en que se realice dependerá de la aplicación o de la efectividad de cada método según la aplicación.

En la siguiente imagen se observa paso a paso cómo es el proceso de balanceo de una batería. Partiendo de la batería totalmente descargada (a), se conecta el cargador y tras un tiempo de carga se llega a unas tensiones dispares entre las celdas (b), desde ese momento se puede comenzar el balanceo mientras continua la carga del pack completo, provocando que las celdas de mayor carga disipen parte de la corriente entrante. Cuando la tensión de alguna celda llegue al límtite superior, se detiene la carga, mientras se sigue balanceando y descargando las celdas de mayor tensión. En el momento en el que esas celdas bajen ligeramente su tensión, se podría conectar el cargador de nuevo, pero para evitar la contínua conexión y desconexión del cargador, es recomendable volver a conectarlo cuando se hayan bajado las tensiones un cierto umbral o hayan sido igualadas a la mínima (d).

Figura 3-8. Ejemplo de proceso de balanceo

Con las tensiones igualadas en (d) se continua la carga, y tras un breve periodo de tiempo probablemente se vuelva a producir una situación similar a la (b) con las tensiones desigualadas, es por eso que el balanceo se considera un método iterativo, que no cesa hasta que se complete la carga completa de todas las celdas.

Debido a que las corrientes de fuga en circuito abierto de cada celda son distintas, una batería nunca permanece balanceada con el paso del tiempo, por tanto, el balanceo debe ser realizado siempre que se produzca una carga, tratando de cargar periódicamente la batería para que no haya mucha dispersión en el SOC de las celdas.

## 3.2.2 Criterio de diseño

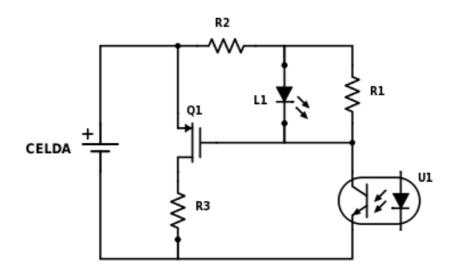

Como antes se ha mencionado, por la facilidad de implementación, el balanceo pasivo ha sido la opción elegida en nuestro caso, cuya circuitería se explicará al detalle en el siguiente punto. Dado que el circuito de balanceo maneja una corriente considerable comparada con el resto de subsistemas, se ha aislado galvánicamente del microcontrolador, evitando cualquier corriente que pudiese llegar a destruirlo. Se ha dimensionado la resistencia conforme a que diese la máxima corriente posible sin necesidad de recurrir a empaquetados no SMD extremadamente grandes, con una disipación de casi 2W por cada celda en serie y una corriente de hasta 0.42A.

18 Gestión de baterías

## 3.2.3 Circuito de balanceo

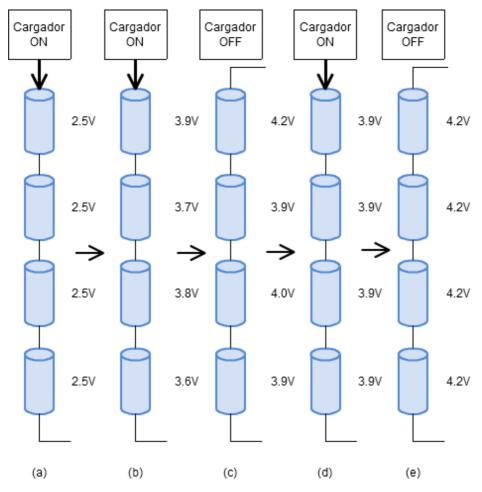

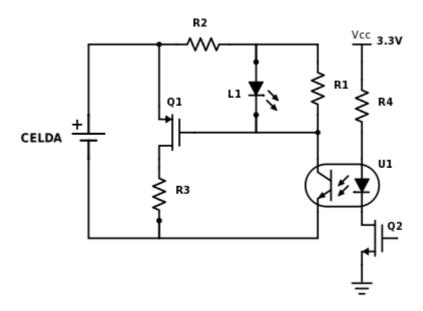

El circuito usado para el balanceo está basado en unos apuntes de la Universidad de Málaga de la asignatura Electrónica del Vehículo Eléctrico en los que se desarrolla un pequeño BMS basado en Arduino. El circuito previo a su aislamiento galvánico es el siguiente:

Figura 3-9. Circuito de balanceo

Siendo

$R3=10\Omega$

$R2=330\Omega$

$R1=560k\Omega$

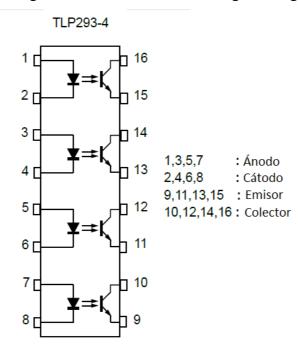

U1: Optoacoplador Toshiba TLP293-4

Q1: PMOS FDN304P L1: Diodo LED naranja

Como se observa, la celda se dispone en pararelo con la resistencia de disipación R3 y un PMOS, cuyo objetivo es abrirse o cerrarse según conduzca o no el transistor del optoacoplador, actuando como un interruptor.

El diodo L1 sirve como indicativo externo de que el circuito está balanceando, puesto que cuando el MOSFET entra en corte el led también lo hace, y cuando Q1 entra en Saturación el LED conduce.

La resistencia R1 es la única diferencia respecto al circuito propuesto por los apuntes, dado que sin dicha resistencia las corrientes parásitas de Q1 no conseguían retornar cuando el transistor del optoacoplador estaba en corte.

Cuando el transistor de U1 está en corte, L1 y Q1 entran en corte también, por lo que  $V_G = V_S = 0V$  y se cumple la condición de corte de Q1. Siendo  $V_T = -0.8V$

$$V_{SG} < -V_T$$

Al cerrarse el transistor de U1, el diodo conduce y Q1 entra en saturación, y gracias a la baja  $R_{DS(ON)}$  (del orden de  $60 \text{m}\Omega$ ) el comportamiento es similar a un cortocircuito en el MOSFET, dejando que casi toda la corriente pase por la resistencia de disipación R3 y se produzca el balanceo. El dimensionamiento de R3 se hizo para no sobrepasar los 2W, potencia máxima soportada por el empaquetado 2512. Despreciando  $R_{DS(ON)}$  y a la máxima tensión que una celda puede dar, la corriente máxima que puede balancear sería:

$$I = \frac{V}{R} = \frac{4.2}{10} = 0.42A$$

Y la potencia disipada en ese caso:

$$P = \frac{V^2}{R} = 1.764W$$

Dado que el optoacoplador requiere una corriente mínima en el lado del diodo para que el transistor conduzca, 10mA mínimo según recomienda Toshiba en su datasheet, se ha situado una resistencia en Pull-Up en el ánodo de dicho diodo, alimentada a 3.3V, y que dada la tensión en directa del diodo  $V_F$  = 1.1V queda su dimensionamiento:

$$R = \frac{V_{DD} - V_F}{I} = \frac{3.3V - 1.1V}{0.01A} = 220\Omega$$

Para controlar el régimen de conducción o corte de cada optoacoplador, se ha dispuesto en el cátodo del diodo un expansor de entradas/salidas, el cual puede ser configurado como entrada o como salida en drenador-abierto como se observa en la figura.

Figura 3-10. Puerto del expansor de E/S

De manera que alternando el valor del puerto de salida del expansor conseguiremos un control absoluto sobre la conducción o el corte del optoacoplador y, por ende, el control absoluto del circuito de balanceo.

20 Gestión de baterías

Figura 3-11. Esquema completo del circuito de balanceo

Aclarar que obviamente Q2 pertenece a uno de los expansores de E/S, no es un MOSFET independiente, y que se han usado expansores de E/S para no utilizar demasiadas salidas digitales del microcontrolador, ya que en la PCB hay 16 circuitos iguales al representado aquí arriba. Mediante el expansor podemos comunicarnos por el bus SPI ya usado con los ADCs y sólo requiere de un CS más, economizando al máximo los pines del  $\mu$ C.

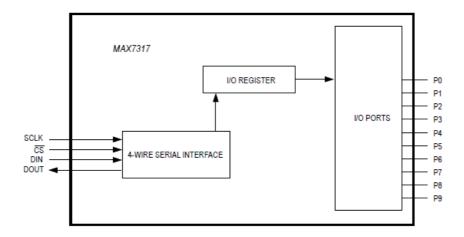

Los expansores utilizados son los MAX7317, de 10 puertos cada uno, por lo que se han usado dos. Se eligió este modelo por la sensillez de la codificación, ya que con el cambio de un solo bit se conmuta el nivel de la salida entre alto y bajo. También se eligió porque opera en el mismo rango de tensiones que el µC, lo que hace posible la transmisión SPI sin necesidad de ningún adaptador de tensiones.

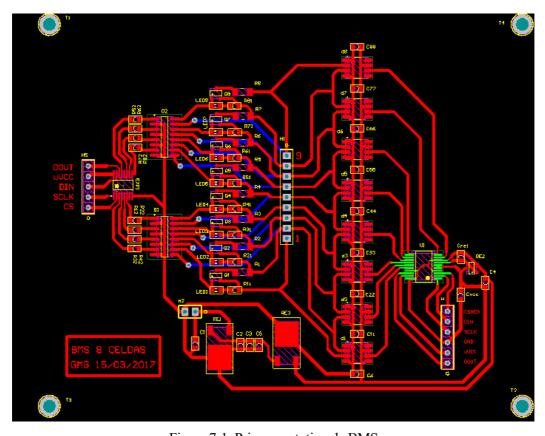

# 4 DESARROLLO HARDWARE

N este capítulo se incluirán el resto de subsitemas y partes del harware que no pertenecen a la gestión la batería o no han sido anteriormente explicadas, tratando de dar una visión más completa y estructurada de cada PCB. El desarrollo de las PCBs se ha realizado en Altium Designer 14.3 y se ha evoluciado mediante el prototipado y la corrección de errores, siendo el aquí expuesto el cuarto y último prototipo realizado. Los enrutados de las PCBs se han realizado a dos caras y tratando de minimizar el tamaño de la placa.

# 4.1 Módulo esclavo

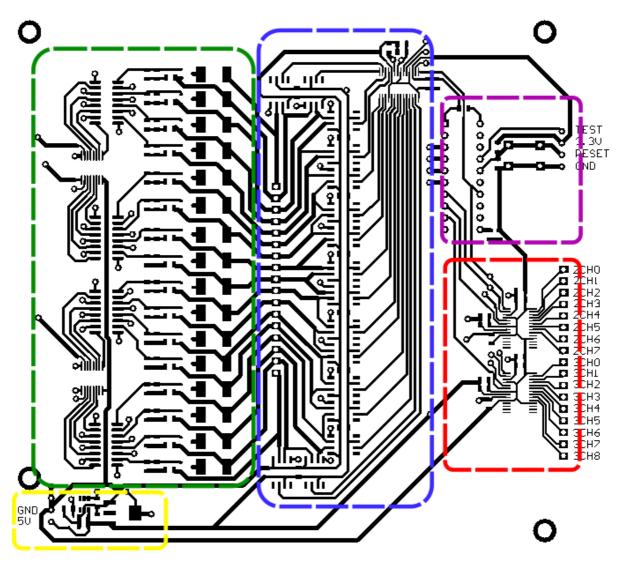

Para facilitar la tarea de estructuración de la PCB y todas sus partes, a continuación se presenta un diagrama con el enrutado dividido en las secciones que trataremos a continuación.

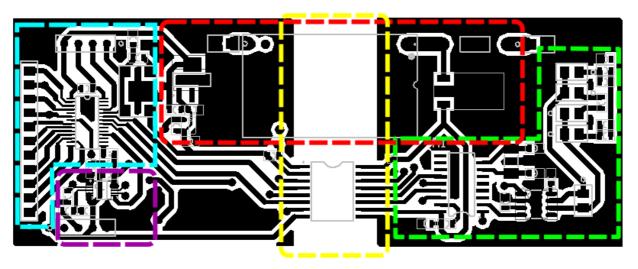

Figura 4-1. Subsistemas PCB Slave

Desarrollo hardware

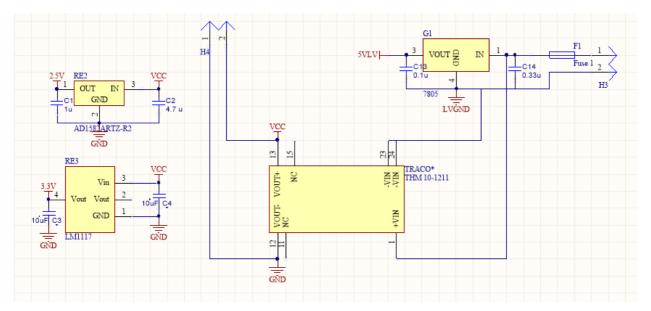

### 4.1.1 Circuito de alimentación

El circuito de alimentación se corresponde con la parte bordeada de amarillo en la figura 4-1. La entrada de alimentación de las PCBs se produce a 5V distribuidos por el Maestro a cada uno de los BMS Esclavos. Dado que en cada Esclavo se requieren más tensiones de alimentación o referencia que los 5V, exiten tres dispositivos reguladores para satisfacerlo.

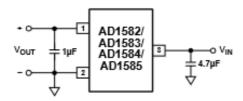

El AD1582 es una referencia de voltaje que convierte 5V de entrada en 2.5V y proporciona la tensión de referencia de todos los ADC de la PCB, funciona mediante una retroalimentación cerrada por sus condensadores de alimentación de  $1\mu F$  y  $4.7~\mu F$ .

Figura 4-2. Diagrama de conexión típica del AD1582

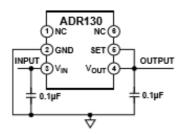

El ADR130 es otra referencia de voltaje del fabricante Analog Devices, que convierte una tensión de entrada de entre 2V y 18V a una tensión de salida configurable, ya sean 1V o 0.5V. En nuestro caso, y como se explicó en el apartado 3.1.2, los ADs necesitarán una referencia de 0.5V que consiguiremos uniendo el pin 5 de SET al pin 4 de VOUT. Requiere también de un condensador de  $0.1\mu F$  a la entrada y salida.

Figura 4-3. Diagrama de configuración del ADR130

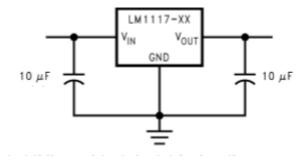

Por último, y para conseguir la tensión de 3.3V necesaria para las resistencias de Pull-up, para la alimentación del microcontrolador y para los expansores de E/S, usaremos el regulador de tensión LM1117 en su versión de salida fija de 3.3V de Texas Instruments. Al igual que los dos anteriores, require los siguientes condensadores a la entrada y salida.

Figura 4-4. Diagrama de funcionamiento básico del LM1117

La PCB al completo está diseñada para economizar al máximo el espacio disponible debido a las altas limitaciones espaciales en el interior del monoplaza, el circuito de alimentación es una prueba de ello, ocupando todo lo anterior menos de 25 x 13mm. La localización del circuito ha sido elegida para estar lo más cerca posible del acceso a las pistas de 3.3V de los expansores y 5V de los AD.

El GND utilizado en toda la PCB y al que están referenciados los planos de tierra son el mismo para todos los Esclavos, que es el que otorga la salida del convertidor DC/DC del Maestro.

#### 4.1.2 Subsistema de Balanceo

Corresponde con la parte cercada por el cuadrado verde en la figura 4-1. Pese a que la mayoría de los aspectos ya han sido mencionados en el apartado 3.2.3, hay ciertos detalles que antes no han sido explicados.

El IC usado para los optoacopladores es el TLP293-4, cada uno contiene cuatro optoacopladores independientes entre sí en su interior. Dado que se necesitan 16 circuitos resistivos para el balanceo, se necesetarán 4 circuitos integrados como el mostrado en la siguiente figura.

Figura 4-5. Esquema interno TLP293-4

La disposición en la que se conecta cada una de las patas sigue el esquema de U1 representado en la figura 3-11, tratando cada optoacoplador de forma independiente.

Entre cada dos TLP293-4 se dispone un expansor de E/S MAX7317 comunicado por SPI con el microcontrolador. El expansor está alimentado por los 3.3V dispuestos por el LM1117, con un condensador opcional de  $0.047\mu\text{F}$  entre  $V^+$  y GND.

Figura 4-6. Esquema interno MAX7317

Los pines SCLK, DIN, CS y DOUT son los asignados para la comunicación SPI, dejando el DOUT o MISO sin unir el bus por motivos que se explicarán en el apartado 5 de Comunicaciones.

El circuito resistivo de cada celda ha sido compactado lo más horizontalmente posible para conseguir una disposición espacial ordenada, facilitando el conexionado. En la cara trasera, no apreciable en la figura 4-1, se han unido mediante vías las conexiones imposibles de realizar en la cara delantera por los numerosos cruces entre pistas.

Las resistencias usadas en el circuito han sido todas SMD de métrica 0805 por su reducido tamaño, excepto las resistencias de disipación de corriente (R3 en la figura 3-11), que son de métrica 2512 para disipar mejor el calor de la corriente pasante. Las pistas que reccore la corriente balanceada se han fabricado con un ancho de 35mils.

El P-MOS usado ha sido diseñado para aplicaciones especiales de gestión de baterías, con lo cual soporta corrientes de hasta 10A en forma de pulsos y 2.4A de forma continuada, más que suficiente para la carga a la que será sometido.

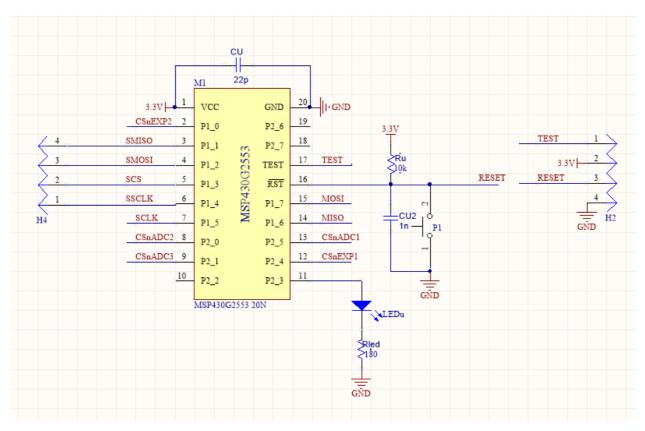

## 4.1.3 Microcontrolador

El microcontrolador del *Slave* y todo lo necesario para su funcionamiento está recogido por el recuadro rojo en la figura 4-1. El MSP430G2553 ha sido el elegido en su versión de 20 pines en formato DIP, por si fuese necesaria su extracción y uso en la launchpad.

El MSP430G2553 cuenta con unas características suficientes para nuestro uso:

- 16 MHz de frecuencia de reloj

- 24 pines GPIO

- 0.5 KB de RAM

- 16KB de memoria no volátil

- 2 puertos SPI

- Rango de alimentación de 1.8V a 3.6V

Para el uso del  $\mu$ C sin el launchpad el fabricante recomienda [3] una resistencia en Pull-Up de  $10k\Omega$  en el pin de RESET, un botón de RESET en paralelo a un condensador de 1nF y un condensador de 22pF entre 3.3V y GND, como se observa en la figura 4-7.

Los dos puertos SPI son fundamentales puesto que se usará el puerto de la USCI\_B (P1\_5, P1\_6 y P1\_7) para la comunicación como *Master* con los periféricos de la PCB y el puerto de la USCI\_A (P1\_1, P1\_2 y P1\_4) para la comunicación como *Slave* con el BMS *Master*. En total, y sumando los 3 pines fundamentales del bus SPI (SCLK, MISO, MOSI) el SPI\_B necesita 8 pines para la comunicación con los cinco periféricos de la PCB (EXP1, EXP2, ADC\_Volt, ADC\_Temp1, ADC\_Temp2), mientras que el puerto SPI\_A sólo necesita los 3 fundamentales y uno de entrada del Chip Select, que se introducen a la PCB por el puerto H4.

Para la programación del  $\mu$ C "on board" son necesarios 4 pines de salida de la PCB que puedan ser conectados con unos jumpers de la launchpad, como muestra la figura 4-7 son el pin de TEST, RESET, 3.3V y GND del puerto H2.

Figura 4-7. Esquemático del subsistema del MSP430G2553

Por último, como se puede observar en el pin 2\_3, se ha instalado un led multipropósito, con el objetivo de usarlo como indicador siempre que fuese necesario o como señal en caso de error.

## 4.1.4 Subsistema de temperatura

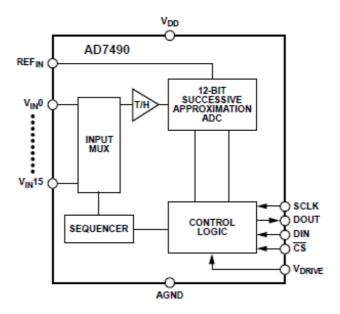

Correspondiente a la zona con el borde rojo de la figura 4-1. En la PCB el único hardware de dicho subsistema es la entrada de los sensores analógicos a los ADCs.

Los ADCs usados son los AD7490, son convertidores de aproximaciones sucesivas de 12 bits y 16 canales, con empaquetado TTSOP de 28 pines y un tamaño muy reducido. Necesitan además de VDD y GND, una referencia de valor igual a la mitad de la alimentación (usaremos los 2.5V proporcionados por el AD1582) y una tensión  $V_{DRIVE}$  a la que transmitirá el bus SPI, sin necesidad de un aislador digital o un adaptator.

Desarrollo hardware

Figura 4-8. Esquema de funcionamiento AD7490

Para el correcto funcionamiento del AD7490 son necesarios unos condensadores para el suavizado de las tensiones de referencia, alimentación y drive:

- Un condensador de 10μF en paralelo con otro de 0.1μF entre VDD y GND

- Un condensador de  $10\mu\text{F}$  en paralelo con otro de  $0.1\mu\text{F}$  entre  $V_{DRIVE}$  y GND

- Un condensador de  $0.1\mu\text{F}$  entre  $REF_{IN}$  y GND, lo más cerca del ADC posible

Así como también es necesario la unión entre sí de las 5 entradas de AGND existentes, según especifica el fabricante en la hoja de datos [4].

Por el puerto H5 entran las 16 entradas de tensión de los sensores, ampliables a 32 cambiando el conector y enrutado. Dado que los ADCs pueden leer una entrada de entre 0 y 5V, el modelo del sensor de temperatura puede ser intercambiado por otro con el mismo rango de tensión analógica de salida.

Figura 4-9. Esquemático del subsistema de temperatura

# 4.1.5 Subsistema de voltaje

Por último, y contenido por el recuadro azul en la figura 4-1, el subsistema de monitorización de voltaje, que como se explicó en el apartado de gestión de baterías, basa su grueso en los amplificadores diferenciales LT1990A.

La tensión de salida de cada uno de los 16 ADs entra directamente al AD7490, que tiene las mismas consideraciones para su funcionamiento que las explicadas en el apartado anterior.

Únicamente son necesarios 8 condensadores entre VCC y GND de  $0.1\mu F$  para los ADs, con un condensador por cada dos LT1990A.

En la figura 4-10 se expone una parte representativa del esquemático del subsitema.

28 Desarrollo hardware

Figura 4-10. Esquemático del subsistema de voltaje

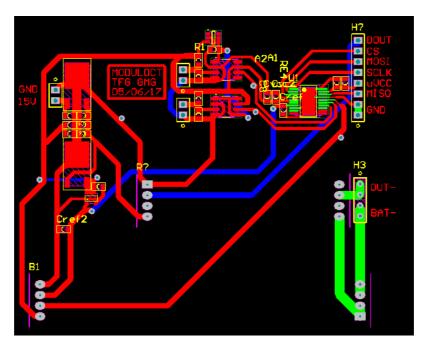

# 4.2 Módulo del Maestro

El siguiente esquema presenta la cara superior del enrutado de la PCB del Maestro, se han dividido los subsistemas por colores y se han mantenido los planos de tierra, a diferencia que en el anterior esquema.

A la izquierda en la cara superior, el plano es de VCC, en la cara inferior reside el plano de GND. A la derecha los planos son de LVGND en ambas caras.

Figura 4-11. Subsistemas PCB Master

# 4.2.1 Subsistema de intensidad

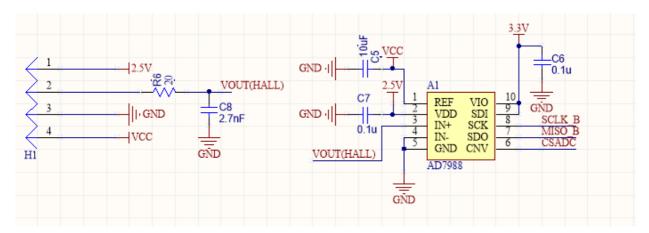

Se corresponde en la PCB por la zona remarcada en violeta en la figura 4-11. Está compuesta por el puerto H1, que cede la alimentación y referencia al sensor FEM, y contiene su salida. Mediante un filtro RC la señal analógica del sensor entra en el AD7988-5, un ADC monocanal de 16 bits.

Figura 4-12. Esquemático subsitema de intensidad

A diferencia de la mayoría de ADCs, la alimentación y la referencia del AD7988-5 son independientes entre sí, siendo su alimentación 2.5V y la referencia la que marca el rango de tensiones de entrada (5V en nuestro caso). Ambas tensiones necesitan un condensador respecto a GND como se observa en la figura 4-12, que serán de  $0.1\mu F$  y  $10\mu F$  respectivamente.

El AD7988-5 nos brinda la posibilidad de una entrada diferencial de tensión entre  $IN^+$  y  $IN^-$ , aunque en nuestro caso no es necesaria, por lo que la entrada negativa se ha conectado a GND.

Para la selección del modo CS, que nos permite la comunicación por SPI, el pin 9 de SDI debe estar unido con VIO, que será la tensión a la que se realizará la comunicación.

# 4.2.2 Aislamiento galvánico

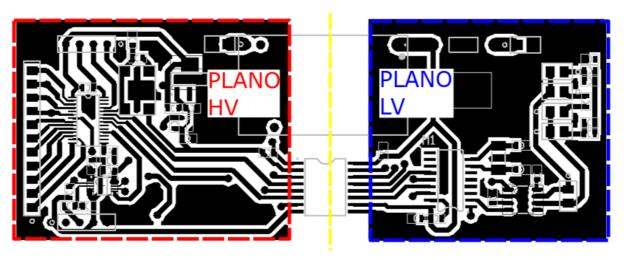

Una de las restricciones más importantes en la normativa de FSAEE en la elaboración del BMS y otras PCBs es la obligatoriedad de un aislamiento galvánico entre el sistema tractor y el sistema de baja tensión.

El sistema de LV del coche proviene de una batería de litio de 12V que alimenta la mayoría de los subsistemas electrónicos. El sistema tractor queda definido como aquel que proporciona potencia al vehículo o esté en contacto con cualquier elemento de HV, puesto que en cada Slave los ADs están en contacto directo con las celdas midiendo su tensión y están alimentados a VCC y GND, todo lo existente en esas PCBs se considera parte del sistema tractor según la normativa.

Además del aislamiento galvánico, si los sistemas comparten PCB deben cumplir el siguiente requisito:

[5] "EV4.1.7 Cuando el sistema GLV y sistema tractor coincidan en la misma PCB, debe de indicarse claramente en qué parte está cada sistema y habrá que dejar un espacio entre los componentes de cada uno:"

Desarrollo hardware

| Tensión        | En PCB  | Aire   | Con Aislamiento |  |

|----------------|---------|--------|-----------------|--|

| 0 – 50 V DC    | 1.6 mm  | 1.6 mm | 1 mm            |  |

| 50 – 150 V DC  | 6.4 mm  | 3.2 mm | 2 mm            |  |

| 150 – 300 V DC | 9.5 mm  | 6.4 mm | 3 mm            |  |

| 300 – 600 V DC | 12.7 mm | 9.5 mm | 4 mm            |  |

Dado que la batería de HV del monoplaza ronda los 540V, será necesario el mayor espaciado de la tabla. El espaciado de 12.7mm (o 0.5 pulgadas) debe distinguir dos planos de alimentación aislados entre sí, a la izquierda, un plano de VCC que sirve de alimentación de los Slaves y por tanto está en contacto con el sistema tractor, a la derecha el plano de tierra del sistema de LV.

Figura 4-13. Separación de los planos de alimentación

Para conseguir 5V y 0V (nombrados VCC y GND durante todo el documento) en el plano de HV, se ha utilizado un convertidor DC/DC con aislamiento galvánico. Los valores entrantes en el convertidor han sido 12V y 0V (distintos a los 0V de salida), directamente desde el sistema de LV, que han sido nombrados LV12 y LVGND respectivamente, para facilitar la comprensión.

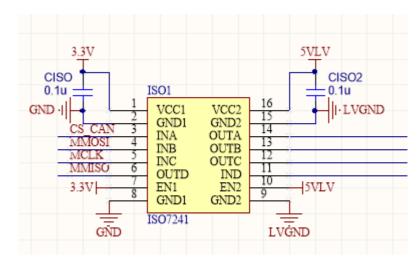

Dado que el BMS necesita comunicarse por CAN con el resto del vehículo, se han aislado las señales digitales procedentes del  $\mu$ C hacia el módulo de CAN mediante un aislador digital ISO7241C, que permite la comunicación por SPI sin contacto entre señales.

El ISO7241C es un dispositivo que proporciona entradas y salidas separadas por una barrera de aislamiento de dióxido de silicio, además de alimentaciones separadas a cada lado del aislamiento, que permiten la comunicación digital a diferentes tensiones: 5V-5V, 5V-3.3V, 3.3V-3.3V y 3.3V-5V. Su variante C proporciona además filtrado en las señales de entrada, para la eliminación del ruido.

Figura 4-14. Esquemático ISO7241C

Para su correcto funcionamiento sólo son necesarios unos condensadores de  $0.1\mu F$  entre la alimentación de cada lado y su respectiva referencia. Así como el pin de EN de cada lado a nivel alto para habilitar las salidas.

## 4.2.3 Circuito de alimentación

El circuito de alimentación de la PCB está delimitado por el recuadro rojo de la figura 4-11 y comprende cuatro dispositivos. El regulador LM1117, la referencia de voltaje AD1582, el convertidor DC/DC THM 10-1211 y el regulador LM7805.

Figura 4-15. Esquemático del circuito de alimentación

El LM1117 y el AD1582 ya han sido explicados anteriormente en el apartado 4.1.1, el único matiz que es digno de mención es que su entrada en este caso es la salida del convertidor DC/DC y que por tanto pertenecen al lado de HV de la PCB.

Desarrollo hardware

El convertidor DC/DC elegido es el THM 10-1211, de la marca TRACOPOWER, que se encarga de la regulación de 12V de entrada a 5V, además del aislamiento galvánico entre cada una. Este modelo en concreto es un modelo de la serie THM dotado de altas capacidades de aislamiento (hasta 5000 VACrms) y alta eficiencia (85.5%). No requiere de acondicionamiento externo para su funcionamiento, y tiene empaquetado DIP24. Se ha escogido el modelo de 10W, que proporciona 2A a la salida, en base al cálculo de consumo máximo y un sobredimensionado margen de seguridad.

Ante la entrada del Traco y para su protección se ha predispuesto un fusible, que cortará la corriente en caso de cualquier fallo en el sistema de LV o sobreintensidad.

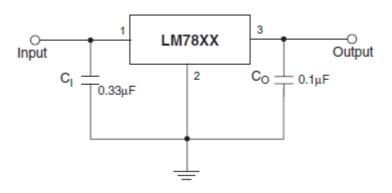

Por último, y para alimentar todos los ICs del subsistema de comunicación CAN, se ha utilizado un regulador de 12V a 5V en el lado del plano de LV, el LM7805 de Texas Instruments. Que únicamente necesita un condensador a la salida y a la entrada de 0.1μF y 0.33μF respectivamente.

Figura 4-15. Diagrama de conexión típica del LM7805

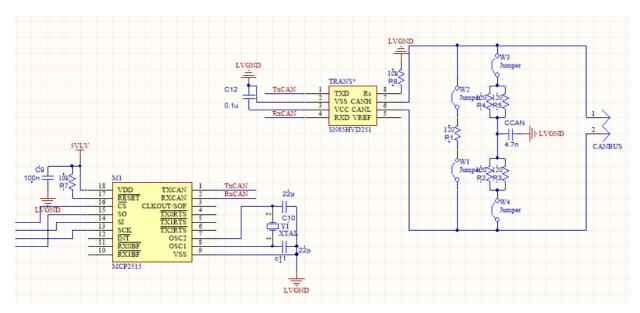

#### 4.2.4 Subsistema de comunicación CAN

Todo lo necesario para comunicar por CAN está contenido por la línea verde en la figura 4-11. Como se observa está en la zona de alimentación de LV, y tal y como se ha dicho en el apartado anterior, las señales provienen del aislador digital.

El primer elemento del sistema es el controlador CAN 2.0B MCP2515, que permite la transmisión y recepción de datos estándar y extendidos y se comunica con el  $\mu$ C del *Master* mediante SPI por los pines CS, SO, SI y SCK. Alimentado a 5V con un condensador de 0.1 $\mu$ F conectado a LVGND y una resistencia en Pull-Up al pin de RESET. Entre OSC2 y OSC1 necesitaremos colocar en configuración en estrella dos condensadores de 22pF y un cristal de 16MHz que actue como reloj del sistema. La salida del controlador son las señales TXCAN y RXCAN que van directamente al transceiver.

Figura 4-17. Esquemático del subsistema CAN

El transceiver SN65HVD251 supone el intermediario entre el bus y el controlador CAN, permitiendo establecer el conjunto de estándares ISO11898. Mediante el pin 8 se puede configurar el modo de operación, alta velocidad conectando el pin a tierra, control de pendiente mediante una resistencia o bajo consumo si está a nivel alto. Su salida se conecta directamente al bus.

La circuitería con jumpers que se observa después del transceiver nos permiten la configuración del bus según se quiten o pongan los jumpers, permitiendo configurar el bus en modo normal (impedancia de  $120\Omega$ ) o modo estrella con terminaciones divididas para rechazar el modo común, tal y como indica el fabricante en la hoja de datos.

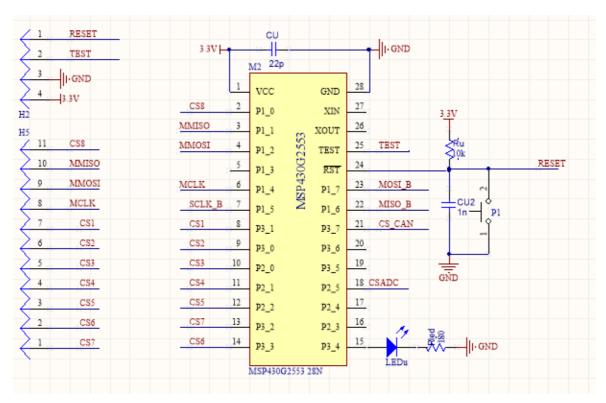

# 4.2.5 Microcontrolador y comunicación SPI

Por último, los componentes del microcontrolador del Maestro quedan recogidos en el recuadro azul de la figura 4-11. Aunque presenta muchas similitudes con el subsistema microntrolador de los *Slaves* hay ciertas diferencias que conviene destacar. En este caso el μC elegido también ha sido el MSP430G2553, pero lo ha sido en su versión de 28 pines que proporciona un puerto más (P3\_x) albergar los numerosos CS que se van a manejar.

Su alimentación, condensadores, led multipropósito y puerto para programación permanecen igual que en el caso anterior. En esta ocasión se ha elegido el encapsulado TSSOP-28, dado que el espacio en la PCB del Master es considerablemente más reducido.

Desarrollo hardware

Figura 4-18. Esquemático del Microcontrolador

Como se observa en la imagen, el puerto de la USCI\_A será utilizado para la comunicación SPI con los 8 Slaves y el módulo de CAN, mientras que el puerto de la USCI\_B está dedicado exclusivamente al ADC del sensor de intensidad.

# **5 COMUNICACIONES**

N el apartado de comunicaciones se explicará detalladamente lo necesario para conocer el protocolo SPI, así como las consideraciones que han sido necesarias para las comunicaciones con cada sistema y la codificación en los mismos.

# 5.1 Introducción al protocolo SPI

El protocolo SPI (del inglés Serial Peripheral Interface) es un estándar de comunicaciones síncrono en serie usado principalmente para transferir información entre circuitos integrados a corta distancia. El protocolo fue desarrollado por Motorola a finales de los años 80 y se ha convertido en un estándar *de facto* por extendido uso y antiguedad.

La comunicación en SPI es completamente bidireccional con una arquitectura Maesto-Esclavo. El Maestro determina cuándo se va a comunicar, con quién lo va a hacer y a la frecuencia a la que lo va a hacer. Los dispositivos con más de un Esclavo están regulados a través de una linea de selección de Esclavos (Chip Select ó Slave Select).

Figura 5-1. Ejemplo de SPI con un Maestro y un Esclavo

El bus SPI está compuesto por un mínimo de cuatro señales:

- SCLK: Reloj o pulso que marca la sincronización. Cada pulso se lee o se envía un bit.

- MOSI (Master Output Slave Imput): Salida de datos del Maestro y entrada al Esclavo.

- MISO (Master Imput Slave Output): Entrada de datos al Maestro y salida del Esclavo.

- CS/SS (Chip/Slave Select): Selección de un Esclavo y/o activación del mismo.

La información es enviada de manera síncrona con los pulsos de reloj, es decir, con cada pulso se envía un bit. Para que comience la transmisión el *Master* debe poner a nivel bajo el CS del *Slave* con el que se quiere comunicar, con esto, el se activa y comienza a comunicar. La transmisión de información se realiza con el primer pulso del reloj, transmitiendo información por MISO a la vez que lee el primer bit por MOSI, en estas ocasiones el *Slave* transmite basura o bits saturados, por no tener información aún de lo que el *Master* le pide. Cuando el CS vuelve a nivel alto o después de haber acabado la transmisión, el *Slave* tiene la información transmitida por el *Master* y está preparado para enviar lo que le ha pedido en la siguiente transmisión. Por otro lado el *Master* ha obtenido información que no tiene valor, y debe iniciar otra comunicación con el *Slave*. Este es el significado de full duplex, el *Master* comunica a la vez que el *Slave* por distintas lineas.

Los pulsos del reloj pueden estar programados para que la transmisión del bit se realice en cuatro modos diferentes, mediante los parámetros de polaridad y fase.

36 Comunicaciones

Figura 5-2. Configuración de polaridad y fase del reloj

Mediante la polaridad se configura la lectura de información en el flanco de bajada (CPOL=1) o en el flanco de subida (CPOL=0). Mediante la fase se determina el retraso de la transmisión de MISO y MOSI, si CPHA=0 los datos cambian en la mitad del ciclo de reloj de su predecesor, si CPHA=1 se retrasa para que lo hagan justo cuando empieza su ciclo.

Figura 5-3. Ejemplo de SPI con un Maestro y varios Esclavos

Una de las ventajas que presenta el protocolo SPI es la reflejada en el ejemplo de la figura 5-3, en el que un solo *Master* se comunica con varios *Slaves*. Mientras que en muchos protocolos en serie son necesarias varias lineas de comunicación con cada *Slave*, en SPI se comparten SCLK, MISO y MOSI entre esclavos, y el CS define con cual de ellos el *Master* se comunicará en ese momento. Cuando el CS1 está a nivel alto toda la información del bus es inexistente para el *Slave1*, omitiendo su lectura y respuesta.

La transferencia de datos no está limitada a bloques de 8 bits, aunque suele ser lo habitual. Es posible la comunicación en bloques de 16bits, 24bits, etc. Y su implementación hardware es muy sencilla, dado que no requiere de circuitos para hacerla funcionar. Los esclavos no necesitan de su propio reloj puesto que lo proporciona el *Master*.

# 5.1.1 Lógica tri-estado

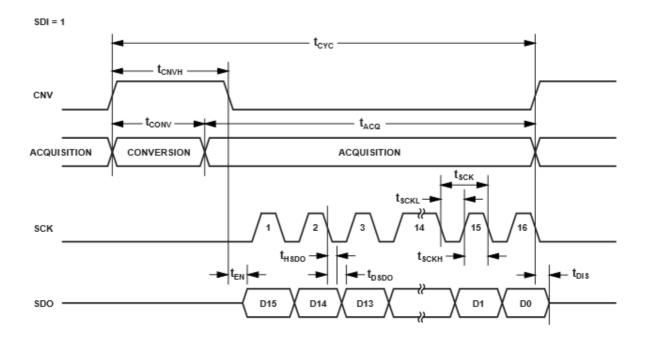

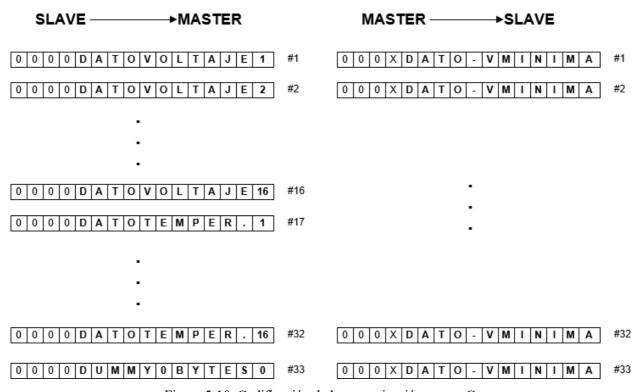

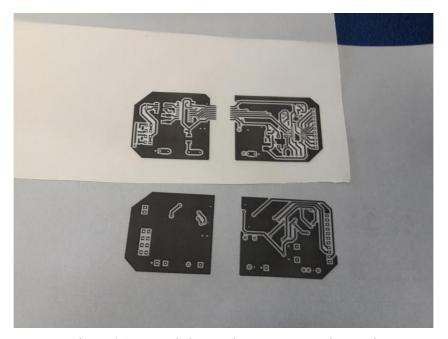

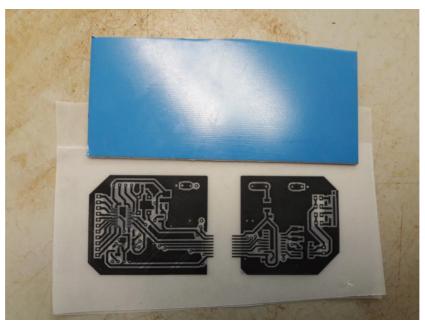

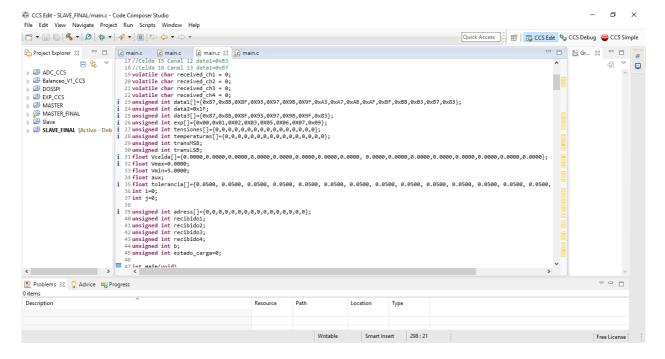

En electrónica digital, la lógica tri-estado permite a un puerto de salida asumir un estado de alta impedancia, lo que le permite permancer lógicamente desconectado del circuito cuando no transmite información.