## UNIVERSIDAD DE SEVILLA ESCUELA SUPERIOR DE INGENIEROS INGENIERO DE TELECOMUNICACIONES

## PROYECTO FIN DE CARRERA

# DISEÑO DE UN CONMUTADOR DE ANTENA A 5 GHz CON HEMT EN TECNOLOGÍA MMIC

Autor: Juan María Rodríguez Sánchez

Tutor: Carlos Crespo Cadenas Enero 2004

Con todo cariño para mi familia, por apoyarme y aguantarme durante estos largos años.

Chi vuoc por termine alli umani ingegni?

GALILEO GALILEI

# **ÍNDICE**

| 1. Introducción                                                                            | 1    |

|--------------------------------------------------------------------------------------------|------|

| 1.1. Situación inicial                                                                     | 1    |

| 1.2. Objeto del proyecto                                                                   | 3    |

| 2. Tecnologías utilizadas                                                                  | 4    |

| 2.1. Tecnología MMIC                                                                       | 4    |

| 2.1.1. Introducción.                                                                       | 4    |

| 2.1.2. Ventajas y desventajas de los MMIC's                                                |      |

| 2.1.2.1. Coste                                                                             |      |

| 2.1.2.2 Prestaciones                                                                       |      |

| 2.1.2.3. Reproducibilidad                                                                  |      |

| 2.1.2.5. Tamaño y manejo.                                                                  |      |

| 2.1.3. Tecnologías MMIC                                                                    |      |

| 2.1.4. Aplicaciones                                                                        |      |

| 2.2. HEMT                                                                                  | 8    |

| 2.2.1. Principios del HEMT                                                                 | 8    |

| 2.2.2. Teoría                                                                              | 9    |

| 2.2.3. Tecnología HEMT                                                                     | 12   |

| 2.2.4. Ruido en el HEMT                                                                    | 14   |

| 2.3. Proceso ED02AH de OMMIC                                                               |      |

| 2.3.1. Componentes utilizados.                                                             |      |

| 2.3.1.1. Transistor de empobrecimiento                                                     |      |

| 2.3.1.2. Capacidades                                                                       |      |

| 2.3.1.3. Inductancias de espiral 2.3.1.4. Resistencias                                     |      |

| 3. Reseña teórica de switches                                                              | . 23 |

| 3.1. Configuración y funcionamiento básicos                                                | 23   |

| 3.2. Switches MMIC con FET's de GaAs                                                       | 25   |

| 3.2.1. Mecanismo de conmutación de un FET de GaAs                                          |      |

| 3.2.2. Circuito equivalente del FET como conmutador                                        |      |

| 3.2.3. Implementación de switches MMIC                                                     |      |

| 3.3. Diferentes configuraciones de switches con FET's                                      | 28   |

| 3.3.1. Switch T/R para comunicaciones personales a 1.9 GHz                                 |      |

| 3.3.2. Conmutadores SPDT MMIC para DC-40 GHz y 20-40 GHz                                   |      |

| 3.3.3. Switch T/R de alta potencia para 2-18 GHz                                           |      |

| 3.3.4. Switch SPDT MMIC usando JFET's de GaAs y modo E/D para comunicaciones personale     |      |

| 3.3.5. Switch SPDT IC en tecnología de GaAs para sistema digital de comunicaciones móviles |      |

| 3.3.6. Switch T/R monolítico de alta potencia para la banda K/Ka                           |      |

| 3.4. Efectos de la no linealidad del switch                                                | 37   |

| 4. Switch A                                                   |     |

|---------------------------------------------------------------|-----|

| 4.1. Base documental del switch                               | 38  |

| 4.1.1. Introducción.                                          |     |

| 4.1.2. Diseño del circuito.                                   |     |

| 4.1.3. Rendimiento                                            |     |

| 4.1.3.1. Efectos del ajuste de la tensión de control          |     |

| 4.1.4. Conclusiones                                           | 41  |

| 4.2. Modificaciones y comentarios teóricos                    | 42  |

| 4.3. Diseño, simulaciones y resultados                        | 45  |

| 4.3.1. Discusión teórica previa                               |     |

| 4.3.2. Simulaciones y resultados                              | 48  |

| 4.3.2.1. Simulaciones del switch con elementos ideales        |     |

| 4.3.2.2. Simulaciones del switch con elementos reales         | 57  |

| 4.4. Conclusiones y solución final                            | 67  |

| 5. Switch B                                                   | 68  |

| 5.1. Base documental del switch                               | 68  |

| 5.1.1. Introducción                                           |     |

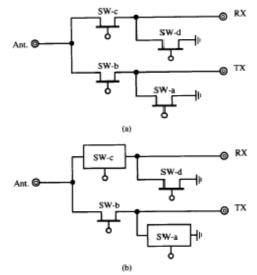

| 5.1.2. Configuración del circuito                             |     |

| 5.1.3. Características del switch integrado                   |     |

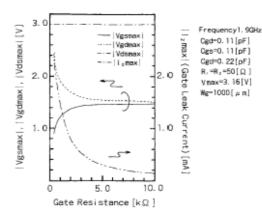

| 5.1.4. Apéndice (cálculo de R <sub>g</sub> )                  |     |

| 5.2. Modificaciones y comentarios teóricos                    | 75  |

| 5.3. Diseño, simulaciones y resultados                        | 76  |

| 5.3.1. Diseño teórico previo                                  |     |

| 5.3.2. Simulaciones y resultados                              |     |

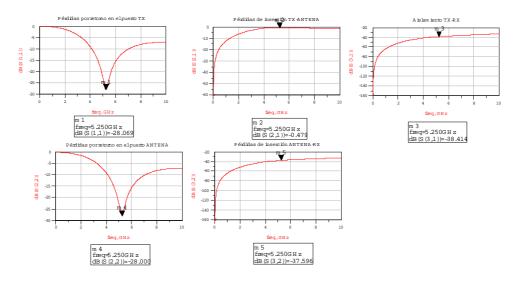

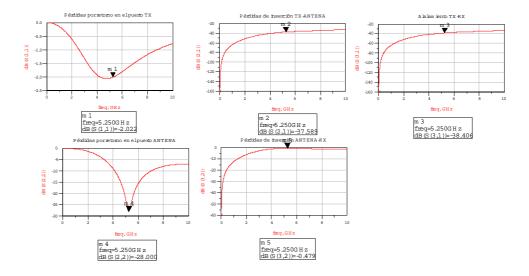

| 5.3.2.1. Simulaciones del switch con elementos ideales        | 80  |

| 5.3.2.2. Simulaciones del switch con elementos reales         | 83  |

| 5.4. Conclusiones y solución final                            | 100 |

| 6. Switch C                                                   | 101 |

| 6.1. Base documental del switch                               |     |

| 6.1.1. Introducción                                           |     |

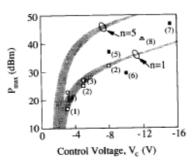

| 6.1.2. Comparación entre potencias máximas transmitidas       |     |

| 6.1.3. Diseño del switch T/R                                  |     |

| 6.1.4. Resultados medidos                                     |     |

| 6.1.5. Mejora de la respuesta en frecuencia                   |     |

| 6.2. Modificaciones y comentarios teóricos                    |     |

|                                                               |     |

| 6.3. Diseño, simulaciones y resultados                        |     |

| 6.3.1. Diseño teórico previo 6.3.2. Simulaciones y resultados |     |

| 6.3.2.1 Simulaciones y resultados                             |     |

| 6.3.2.2. Simulaciones del switch con elementos reales         |     |

| 6.4 Canalucianos y salvaján final                             | 120 |

| 6.4. Conclusiones y solución final                            | 129 |

| 7. Elección final y layout                                                                                                    | 130 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1. Discusión y elección final                                                                                               | 130 |

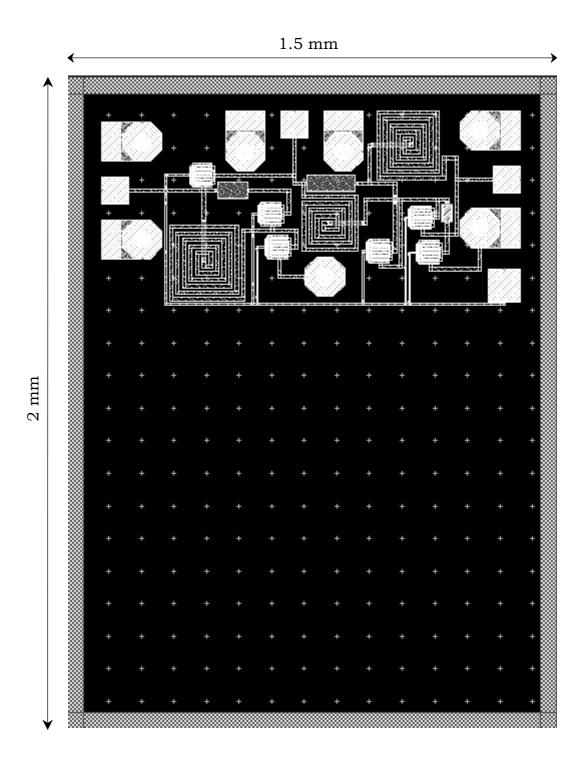

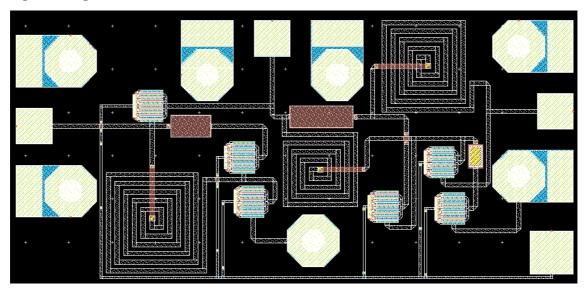

| 7.2. <i>Layout</i>                                                                                                            | 131 |

| 7.2.1. Otro uso del switch: diversidad de antena                                                                              | 140 |

| 8. Referencias y anexos                                                                                                       | 141 |

| 8.1. Referencias                                                                                                              | 141 |

| 8.2. Anexos                                                                                                                   | 142 |

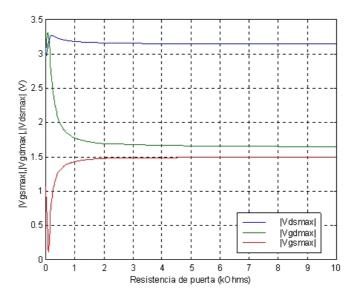

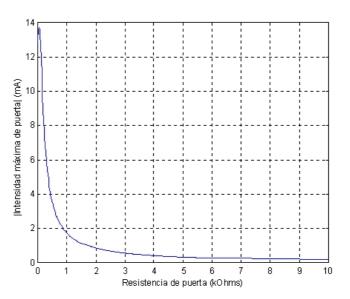

| 8.2.1. Cálculo en MATLAB de las gráficas de I <sub>g</sub> , V <sub>ds</sub> , V <sub>gs</sub> y V <sub>gd</sub> del switch B | 142 |

| 8.2.2. Artículo en el que se basa el switch A                                                                                 | 144 |

| 8.2.3. Artículo en el que se basa el switch B                                                                                 | 147 |

| 8.2.4. Artículo en el que se basa el switch C                                                                                 | 155 |

| 8.2.5. Aspecto de la celda con el <i>layout</i> del circuito                                                                  | 162 |

# 1. INTRODUCCIÓN

### 1.1. SITUACIÓN INICIAL

Las comunicaciones móviles y personales tienen actualmente una enorme importancia en nuestra sociedad de la información. Hoy en día es impensable vivir sin estar comunicado y localizado permanentemente. Esta gran demanda de sentirse en contacto con los demás es lo que ha hecho que en los últimos años la telefonía móvil adquiera una enorme relevancia.

Al igual que en todos los elementos electrónicos, en los dispositivos usados en los terminales móviles siempre se tiende al mínimo tamaño y volumen posible. El avance tecnológico ha contribuido a ir caminando hacia esa meta, y son muchas las tecnologías de fabricación que han aparecido en los últimos años con tres ideas o fines bien marcados: mínimo tamaño, mínimo coste y mínimo consumo. Este último punto es muy importante en el caso de la telefonía móvil, ya que los terminales poseen baterías que, por mucho que han mejorado en los últimos años, tienen una capacidad finita.

Otro aspecto que caracteriza a las comunicaciones móviles en la actualidad es la escasez de espectro radioeléctrico libre, lo que hace necesario la utilización de frecuencias superiores. Esto obliga a usar tecnologías con un muy buen comportamiento a altas frecuencias, tal como la tecnología HEMT.

Para conseguir que los elementos electrónicos que componen los terminales móviles tengan un tamaño lo menor posible y con una gran eficiencia se hace uso de diversas tecnologías de fabricación, entre las que destaca la tecnología MMIC (Microwave Monolithic Integrated Circuit).

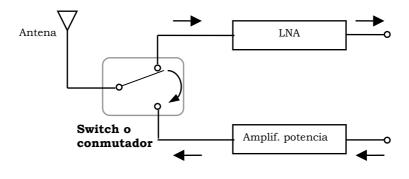

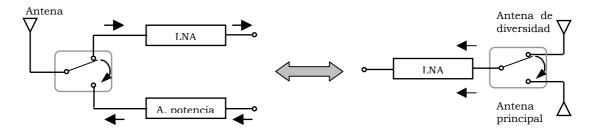

En todo transceptor móvil de radiocomunicación, un elemento importante es el conmutador. Los conmutadores de microondas son elementos esenciales para una amplia variedad de aplicaciones, desde las más sencillas a las más complicadas. Aunque los requerimientos específicos de cada aplicación deben ser adaptadas a necesidades individuales, las características esenciales de los switches descansan sobre la misma base. Todos los conmutadores tienen la misión de dirigir una señal de RF de un camino a otro, con el propósito de compartir una determinada parte del circuito como, por ejemplo, una antena.

Figura 1.1

Hay cinco características fundamentales que se le exigen a un conmutador de antena:

- *Alto aislamiento transmisor-receptor.* Es fundamental para el modo transmisión pues queremos que, cuando se transmita una señal, la mayor

Situación inicial 1

parte posible vaya hacia la antena y muy poca o ninguna hacia el receptor. Es muy importante que sea así ya que normalmente el circuito de recepción siempre está activo y no es deseable que reciba señal del propio transmisor.

- Bajas pérdidas de inserción. Lo deseable es que se pierda muy poca señal en los trayectos transmisor-antena y antena-receptor, por lo que será muy importante la adaptación.

- Capacidad de manejo de grandes potencias. Interesa que el switch no sature a bajas potencias de entrada y sea capaz de, principalmente en transmisión, encaminar señales de gran potencia. En recepción esto no es un problema ya que normalmente se reciben potencias muy pequeñas (<< 0 dBm).

- *Bajo consumo*. Como siempre, ésta es una característica fundamental para todos los dispositivos integrados. Un aspecto importante en este caso es optar por un switch sin tensión de alimentación, simplemente con tensión de control, y preferiblemente, de valor bajo.

- Alta velocidad de conmutación. Lo deseable es que, en los cambios de la tensión de control de *on* a *off* y viceversa, el conmutador pase del modo transmisión al modo recepción y viceversa con un retraso mínimo.

Estos serán nuestros objetivos en la realización de este proyecto, para lo que se hará uso de las diversas técnicas que se nos facilitan.

Situación inicial 2

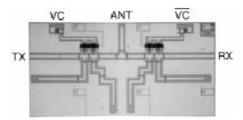

#### 1.2. OBJETO DEL PROYECTO

El proyecto que aquí se presenta muestra el diseño de un conmutador de antena monolítico para una frecuencia de 5.25 GHz. A su vez, se engloba dentro de un proyecto mayor, llamado "Plataforma hardware para comunicaciones móviles de cuarta generación". Este proyecto está siendo desarrollado por el Grupo de Sistemas de Radiocomunicación perteneciente al Área de Teoría de la Señal y Comunicaciones de la Escuela de Ingenieros de la Universidad de Sevilla, y tiene como objeto la realización física de un transceptor a 5.25 GHz para un terminal móvil de última generación. Para ello se ha optado por usar parcialmente tecnología MMIC, y dentro de ésta, tecnología HEMT pseudomórfica. Estas tecnologías son facilitadas por la Foundry OMMIC de Philips, encargada de la realización del monolítico mediante el proceso de fabricación ED02AH.

En cuanto a aspectos más específicos de la presente documentación del proyecto, es necesario hacer notar que se ha estructurado de una forma muy clara: se ha realizado el diseño de tres switches, presentados por diversos artículos, y, una vez realizadas todas las simulaciones, se ha elegido el mejor teniendo en cuenta los aspectos fundamentales nombrados en el apartado anterior. Una vez hecho esto, se ha diseñado el *layout* del circuito elegido y se han vuelto a realizar nuevas simulaciones. Con todo esto, se pretende profundizar en el estudio comparativo de switches, a fin de ver diversas estructuras.

Previo al diseño descrito anteriormente, se realiza un estudio teórico de las distintas configuraciones de switches existentes, así como de las tecnologías usadas para la realización del switch, esto es MMIC Y HEMT.

Para el diseño, simulación y optimización tanto de los esquemáticos como de los *layouts* de los distintos circuitos se ha hecho uso de la herramienta ADS2003A (Advanced Design System), de Agilent Technologies. A este programa se le han incluido las librerías facilitadas por la *Foundry* de todos sus componentes, para su uso en la realización de los conmutadores.

En cuanto a la nomenclatura, cabe destacar que se ha usado de forma indistinta dos denominaciones para el dispositivo: switch T/R, que es una traducción directa de la palabra anglosajona T/R switch o Transmit/Receive switch, y conmutador de antena, que es como se le llama en todos las referencias hispanas.

Objeto del proyecto 3

# 2. TECNOLOGÍAS UTILIZADAS

## **2.1. TECNOLOGÍA MMIC** ([1] y [2])

#### 2.1.1. Introducción

Un circuito integrado monolítico de microondas (MMIC) es un circuito de microondas en el cual los componentes activos y pasivos son fabricados sobre el mismo sustrato semiconductor. La frecuencia de operación se mueve en el rango de 1 GHz hasta superar los 100 GHz, y pueden ser usados un número importante de diferentes tecnologías y circuitos. El término monolítico es necesario para distinguirlo de los circuitos integrados de microondas (MIC's), los cuales son circuitos de microondas híbridos en los que los componentes activos y algunos pasivos son montados como dispositivos discretos en sustratos dieléctricos. En realidad, de forma estricta, a los circuitos monolíticos que trabajan sobre 30 GHz se les debería llamar circuitos integrados monolíticos de ondas milimétricas, pero las numerosas abreviaturas usadas para su asignación, como MMWIC o M³IC, no han recibido la aprobación general.

Actualmente, para el diseño de MMIC's, se dispone de numerosas herramientas CAD. Además, a estos programas se unen las librerías actualizadas de componentes que proporciona cada *Foundry* para la cual se esté trabajando, por lo que se facilita la tarea del diseñador. En nuestro caso concreto, como se ha dicho anteriormente, el programa es ADS2003A de Agilent y la *Foundry* es OMMIC de Philips. No obstante, el diseño de MMIC's es muy diferente al diseño convencional de VLSI, en el cual la herramienta CAD proporciona un alto grado de automatización a la hora de diseñar el *layout*. En el caso del *layout* de los MMIC's, se requiere un grado de esfuerzo mayor en el diseñador, debido a la importancia de las interconexiones con líneas de transmisión.

#### 2.1.2. Ventajas y desventajas de los MMIC's

A continuación se enumeran las ventajas y desventajas de los MMIC's respecto a los MIC's híbridos. Como ventajas:

- Menor tamaño.

- Mayor fiabilidad.

- Coste menor cuando se fabrican grandes cantidades.

- Menos parásitos y mejor reproducibilidad, dando mejor rendimiento, lo cual es muy importante a altas frecuencias.

#### Como desventajas:

- Coste mayor para un número pequeño de unidades fabricadas, debido al más alto consumo de sustrato.

- Mayores pérdidas y ruido.

- Mayor cross-talk.

- Sin posibilidad de ajuste después de la fabricación

- Rango limitado de valores para los componentes como inductancias y capacidades.

- Diseño largo en el tiempo, así como su fabricación.

A continuación veremos los aspectos más importantes enumerados arriba.

#### 2.1.2.1. Coste

El bajo coste es debido simplemente a que de una simple oblea se pueden producir hasta 1000 amplificadores (por ejemplo), cada uno con prestaciones similares y sin requerir sintonización manual y con mínimo trabajo de montaje. Este argumento se mantiene aún más conforme el circuito es más complicado y requiere mayor número de componentes. Sin embargo, en muchos casos es posible utilizar transistores encapsulados sobre un sustrato barato. Usando éstos, los componentes pasivos tales como los filtros y las redes de adaptación tienen un coste muy bajo. Para un circuito que usa unos pocos transistores y con bastante circuitería pasiva, sería muy dificil reducir su coste usando MMIC's.

#### 2.1.2.2. Prestaciones

La mayoría de los dispositivos MMIC tienen que ser producidos en muchas cantidades y no pretenden alcanzar *el estado del arte* en cuanto a prestaciones. Esto puede ser un problema grave para el diseño de amplificadores de potencia y bajo ruido, donde las prestaciones son el principal objetivo. Para alcanzar bajo ruido y alta potencia a menudo es necesario utilizar transistores discretos antes y después usar las partes MMIC. Con un MIC híbrido el diseñador puede elegir el mejor transistor para conseguir el fin, y los transistores pueden ser de diferentes fabricantes. Los transistores discretos pueden tener la longitud de puerta más corta y la estructura de capa activa óptima para su aplicación, sin reparar en otros requerimientos, debido a que el rendimiento (*yield*) es mucho menos importante. Sin embargo, si se usan las mismas técnicas de fabricación para un MMIC complejo tendríamos un rendimiento pobre debido al efecto multiplicativo de los rendimientos de cada transistor en el mismo chip. Para circuitos con baja densidad esto no debería ser un problema, y así, por ejemplo, los circuitos de ondas milimétricas que usan HEMT's deberían dar buenas prestaciones y rendimiento.

Dispositivos especiales, tales como los diodos Gunn, PIN y varactores, son raramente incorporados en procesos MMIC y esto puede provocar complicaciones para el diseñador; por ejemplo, el switch realizado con FET's puede ser un mal sustituto para el realizado con diodos PIN, y el oscilador de ondas milimétricas realizado con tecnología HEMT dará una baja potencia de salida comparado con el realizado con diodo Gunn. Aún así, la mayoría de estas dificultades son absorbidas por las especificaciones de diseño.

#### 2.1.2.3. Reproducibilidad

La reproducibilidad es excelente para los MMIC's debido a que los componentes activos y pasivos son producidos con los mismos pasos de fabricación y usando las mismas máscaras. Además, como las variaciones en los componentes activos y pasivos están referidos a los mismos parámetros físicos (como la resistencia de la capa activa), hay un ámbito considerable de métodos de diseño para maximizar la reproducibilidad y el rendimiento. En comparación, los MIC's híbridos sufren variaciones de un circuito a otro, debido a los emplazamientos de los dispositivos y las conexiones de cables. La mayoría de los circuitos híbridos requieren una posterior sintonización manual de su respuesta, lo que es muy costoso para producciones grandes.

#### 2.1.2.4. Fiabilidad

Los circuitos monolíticos son más fiables que los circuitos híbridos en tanto en cuanto el proceso de fabricación es controlado cuidadosamente. Por ejemplo, el

proceso ED02AH de OMMIC, que se explicará en el apartado 2.3, es un método de fabricación preciso y detallado en el que cada paso está especificado claramente.

#### 2.1.2.5. Tamaño y manejo

Los circuitos monolíticos son muy compactos y esto puede ser una ventaja significativa. En muchas aplicaciones comerciales hay una necesidad creciente de hacer cada vez más pequeños los circuitos de microondas. Por ejemplo, las antenas tipo array pueden llegar a tener muchos cientos de módulos, y los circuitos monolíticos son esenciales para minimizar el tamaño de la antena y su manejo.

#### 2.1.3. Tecnologías MMIC

Los MMIC's usan de forma predominante GaAs por dos razones clave: primero, porque el GaAs tiene mayores velocidad de saturación y movilidad electrónica que el Silicio, lo que lleva a tener dispositivos más rápidos; y segundo, el GaAs puede ser fabricado fácilmente con alta resistividad, lo que lo hace un magnífico sustrato para componentes pasivos de microondas. Debido a esto, el GaAs ha dominado completamente los primeros 15 años del desarrollo de la tecnología MMIC, e incluso ahora la mayoría de los MMIC's lo utilizan. Sin embargo, los MMIC's con Silicio han mejorado mucho y actualmente hay mucha competencia entre ellos en el campo de las heterouniones. Las tecnologías MMIC que se usan actualmente son:

- GaAs MESFET

- GaAs HEMT (convencional y pseudomórfica)

- GaAs HBT

- Silicio Bipolar

- Silicio-Germanio HBT

- InP HEMT

- InP HBT

- IMPATT, diodos Gunn y Schottky

El GaAs MESFET fue el primer transistor de microondas y continúa siendo muy importante para muchos diseños MMIC. Es fácilmente fabricado usando implantación iónica para aplicaciones de gran volumen y tiene unas buenas prestaciones en cuanto a figura de ruido y potencia de salida. La mayoría de las *foundries* ofrecen procesos de 0.5 µm de longitud de puerta, los cuales son útiles para circuitos que operan con frecuencias de hasta 20 GHz. También se han conseguido circuitos que operan a una frecuencia superior a 30 GHz, usando longitudes de puerta aún menores.

El GaAs HEMT (High Electron Mobility Transistor, transistor de alta movilidad electrónica) pseudomórfico ofrece un considerable incremento de la transconductancia respecto al MESFET, y se han conseguido circuitos que operan a frecuencias superiores a 100 GHz, con transistores con longitudes de puerta tan cortas como 0.1 μm. Sin embargo, esta tecnología es menos adecuada que la GaAs MESFET para producciones muy grandes. Esto es debido a que las capas deben ser fabricadas mediante los métodos MBE (Molecular Beam Epitaxy) o MOCVD (Metal Organic Chemical Vapour Deposition), y estos consumen mucho tiempo. Hablaremos de esta tecnología en el siguiente apartado. Este tipo de tecnología es el que usa el proceso ED02AH de OMMIC.

El GaAs HBT (Heterojunction Bipolar Transistor, transistor bipolar de heterounión) tiene algunas ventajas sobre el GaAs HEMT debido a su estructura vertical. Las dimensiones del dispositivo están dadas más por el material y su dopado que por la litografía. Un HBT con una anchura de emisor de varias micras puede ofrecer unas buenas prestaciones a frecuencias de microondas. Es un transistor con

una ganancia muy alta, pero tiene también grandes resistencias y capacidades parásitas. Puede ofrecer gran potencia y eficiencia, pero tiene limitaciones térmicas. Además, al tener una resistencia de base muy grande hace que su figura de ruido sea más grande que la de un HEMT, aunque este aspecto se está mejorando.

La tecnología bipolar de Silicio ha avanzado mucho en los últimos años y con este dispositivo de homounión se han alcanzado frecuencias de hasta 20 GHz. Además, con el HBT basado en Silicio-Germanio se han alcanzado frecuencias de funcionamiento de más de 100 GHz y figura de ruido de menos de 1 dB a 10 GHz.

Para aplicaciones de ondas milimétricas, actualmente la tecnología GaAs HEMT pseudomórfica no tiene rival. De todas formas, se están utilizando también en este campo, aunque de forma muy escasa, IMPATT u osciladores con diodos Gunn y receptores con diodos Schottky.

#### 2.1.4. Aplicaciones

La mayoría de las aplicaciones de los MMIC's se muestran en la tabla 2.1. Las organizaciones espaciales y militares son las que con mayor ahínco han apostado por esta tecnología, y el programa MIMIC en Estados Unidos es buena prueba de ello.

| Civil                    | Militar              | Espacial                 |

|--------------------------|----------------------|--------------------------|

| Satélites TVRO           | RADAR adaptativo de  | Comunicaciones por       |

|                          | fase                 | satélite                 |

| Terminales terrestres    | Guerra electrónica   | Sensores remotos         |

| VSAT                     |                      |                          |

| Teléfonos móviles        | Misiles inteligentes | Radiometría              |

| Comunicaciones LOS       | RADAR de apertura    | Astronomía               |

|                          | sintética            |                          |

| LAN's inalámbricas       | Sensores remotos     | Satélites de órbita baja |

|                          |                      | (IRIDIUM)                |

| Sistemas de fibra óptica | Señuelos             | Array de antenas de      |

|                          |                      | fase adaptable           |

| GPS                      | Altimetros           |                          |

| Tarjetas inteligentes    | Instrumentación      |                          |

| Traspondedores de        | Sistemas de          |                          |

| búsqueda y rescate       | telecomunicación     |                          |

| RADAR anticolisión       |                      |                          |

| Sistemas médicos         |                      |                          |

| Televisión por DBS       |                      |                          |

| HDTV                     |                      |                          |

Tabla 2.1

#### **2.2. HEMT** ([2])

#### 2.2.1. Principios del HEMT

Una desventaja clara del MESFET es que cuando está muy dopado el canal ( $10^{17}$ - $10^{18}$  átomos/cm³) la movilidad se degrada de forma importante. Así, no es posible beneficiarse de la alta movilidad que ofrece el GaAs; los electrones son estorbados por las impurezas del canal. Una forma de evitar esto es el uso de la heterounión. Si se hace una unión de AlGaAs tipo n con GaAs no dopado, los electrones tienden a moverse desde el AlGaAs al GaAs, formando un canal conductor cerca de la interface. Ahora los electrones están separados de las sustancias donadoras y poseen la movilidad del material no dopado aunque su densidad sea bastante alta.

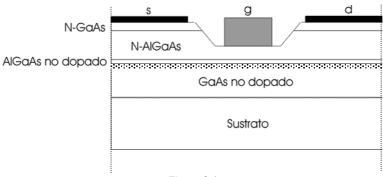

Un refinamiento que a menudo se usa es no dopar el AlGaAs sobre todo el volumen, sino dejar un delgada capa no dopada (de unos 6 nm) adyacente al GaAs. Esto se debe a que los electrones que están en el GaAs pueden verse influidos por el efecto del campo producido por las sustancias donadoras del AlGaAs cerca de la interface. Con este espacio se reduce ese efecto. Se obtiene así una estructura para el transistor como el que se muestra en la figura 2.1.

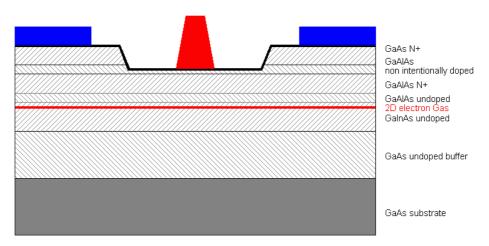

Figura 2.1

El ancho y dopado del AlGaAs tienen que ser diseñados cuidadosamente para que en todos los puntos de polarización la capa de AlGaAs bajo la puerta esté completamente reducida. Si no se produjera esto, resultaría un canal parásito en el AlGaAs con baja velocidad electrónica y consecuentemente malas propiedades de alta frecuencia.

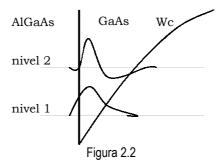

Se produce un efecto mecánico-cuántico que mejora las prestaciones del dispositivo: el pozo de potencial es tan estrecho en el fondo que la forma de onda de los electrones está confinada entre las paredes (figura 2.2) de tal forma que sólo se pueden mover en dos dimensiones. Esto es llamado gas electrónico de dos dimensiones. Estos electrones son diseminados de forma mucho menos importante por las vibraciones de la estructura molecular, por lo que pueden alcanzar grandes velocidades. Estos efectos no son muy fuertes a temperatura ambiente, pero a temperaturas más bajas se muestran claramente.

#### 2.2.2. Teoría

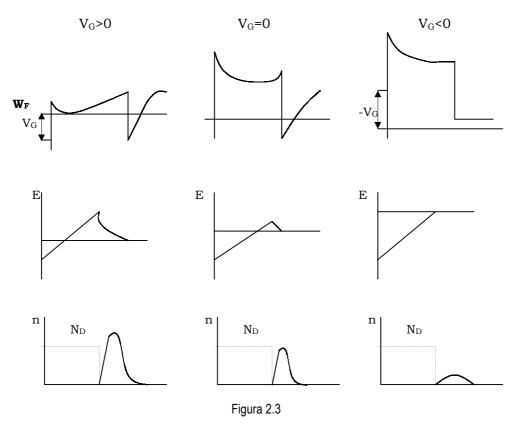

El análisis de un HEMT es simple y complicado al mismo tiempo. La parte simple es evaluada con ayuda de la figura 2.3, donde se representan la densidad de carga, el campo eléctrico y la banda de conducción.

Se ha asumido, como se hace habitualmente, que el nivel de Fermi es  $qV_G$  en la unión metal-AlGaAs. Otra condición que se presupone es que la capa AlGaAs está completamente reducida. Si no fuera así, se tendría un canal parásito en el AlGaAs, donde la velocidad electrónica sería muy baja y las prestaciones del dispositivo se verían fuertemente degradadas, como se comentó anteriormente.

Como el canal conductor es muy delgado, el campo eléctrico pasa de cero en el sustrato de GaAs a un valor finito en el lado AlGaAs de la heterounión. Con ayuda de la ecuación de Poisson el campo en la unión  $E_j$  puede ser relacionado con la densidad electrónica integrada sobre el ancho del canal, la densidad transversal  $n_s$ :

$$E_j = \frac{qn_s}{\varepsilon} \tag{2.1}$$

En la capa de AlGaAs, donde se ha dejado fuera la región de AlGaAs no dopado para hacer el análisis más simple, el campo eléctrico tiene una variación lineal:

$$E = E_j + \frac{qN_D}{\varepsilon}(x - d_{Al})$$

(2.2)

por lo que la posición de mínimo potencial es dada por:

$$d_{Al} - x_{min} = \frac{\varepsilon E_j}{qN_D} = \frac{n_s}{N_D}$$

(2.3)

La profundidad del pozo de potencial respecto al nivel de Fermi es:

$$\Phi W = \Delta W_c - V_{min} - V_2 \tag{2.4}$$

V<sub>min</sub> puede ser expresada en función de V<sub>G</sub>:

$$V_{min} = \phi_B - V_G - V_1 \tag{2.5}$$

$V_1$  y  $V_2$  son los áreas de las regiones triangulares de campo en el AlGaAs:

$$V_1 = \frac{qN_D}{2\varepsilon} x_{min}^2 = \frac{qN_D}{2\varepsilon} \left( d_{Al} - \frac{n_s}{N_D} \right)^2$$

(2.6)

$$V_{2} = \frac{qN_{D}}{2\varepsilon} (d_{Al} - x_{min})^{2} = \frac{qn_{s}^{2}}{2\varepsilon N_{D}}$$

(2.7)

Sustituyendo todo esto en la ecuación (2.4) se obtiene la expresión que relaciona la profundidad del pozo a una tensión de puerta determinada con la densidad transversal:

$$\phi_W = \Delta W_c - \phi_B + \frac{qN_D}{2\varepsilon} d_{Al}^2 + V_G - \frac{qn_s}{\varepsilon} d_{Al}$$

(2.8)

Se observa como la profundidad del pozo se incrementa conforme aumenta la tensión de puerta de forma positiva, pero el incremento es contrarrestado por la densidad transversal cuando el pozo se llena con electrones.

Por otra parte, y ésta es la parte complicada, la densidad transversal en el canal es función de la profundidad del pozo de potencial. Calcular esta dependencia es muy complicado, ya que hay que resolver de forma simultánea las ecuaciones de Poisson y Schrödinger. Cuando la carga electrónica es suficientemente pequeña para ser despreciada, resulta un *pozo triangular*, y para este caso es posible una solución analítica en términos de funciones Airy. Se puede sacar una fórmula aproximada que da las posiciones de las subbandas:

$$W_i \approx \left(\frac{\mathsf{h}^2}{2m^*}\right)^{1/3} \left[\frac{3}{2}\pi q E_j (i + \frac{3}{4})\right]^{2/3}$$

(2.9)

Como era de esperar, los niveles de las subbandas suben cuando el campo aumenta, es decir, cuando el pozo se hace más estrecho. Si asumimos que sólo el nivel de la primera subbanda está por debajo del nivel de Fermi la densidad transversal es dada por la ecuación siguiente:

$$n_s = \frac{1}{\pi} \frac{m_c^* kT}{\mathsf{h}^2} \ln \left[ 1 + \exp\left(\frac{\mathsf{\phi}_W - W_1}{kT}\right) \right] \tag{2.10}$$

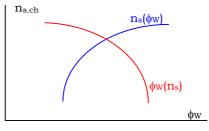

En esta ecuación se puede ver una realimentación negativa de la densidad transversal vía  $E_j$  y  $W_1$ . No obstante, el resultado es el que uno esperaría, un incremento de  $n_s$  con  $\phi_W$ . Como la ecuación (2.8) muestra un decremento de  $\phi_W$  con  $n_s$ , el cruce de las dos curvas dará los valores de ambos (figura 2.4).

Figura 2.4

Si se retoca la ecuación (2.4) con ayuda de la ecuación (2.7), tenemos:

$$\phi_W + \frac{qn_s^2}{2\varepsilon N_D} = \Delta W_c - V_{min} \tag{2.11}$$

Se ve que, si queremos maximizar la densidad transversal  $n_s$ , tenemos que hacer  $\Delta W_c$ - $V_{min}$  tan grande como sea posible.  $V_{min}$  está limitada, tiene un valor positivo mínimo, 4kT/q; de otra forma, los electrones se reunirían en este mínimo y formarían un canal parásito. Por tanto, el valor máximo de  $n_s$  depende principalmente de  $\Delta W_c$ .

Otra forma de verlo es tomar el HEMT como un todo que permanece neutro. Los electrones que se difunden fuera de la capa n-AlGaAs se distribuyen sobre el canal y el metal de la puerta en una proporción que depende de la tensión de puerta. Así, se puede escribir:

$$n_s + n_{gate} = N_D d_{Al} (2.12)$$

donde  $n_{gate}$  es la densidad por unidad de área de puerta. Se observa que  $n_s$  alcanza un máximo cuando  $n_{gate}$  es cero, es decir, cuando el potencial mínimo del AlGaAs está en la puerta. En este caso, la tensión de puerta es:

$$V_{GS} = \Phi_B - \frac{4kT}{q} \tag{2.13}$$

Esta ecuación da un límite superior para la tensión de puerta positiva que puede ser aplicada sin el riesgo de fuga de corriente de puerta.  $\phi_B$  es aproximadamente 0.8 V para la mayoría de los metales de puerta sobre AlGaAs. El canal es reducido al máximo cuando  $n_s \approx 0$ , es decir,  $Ej \approx 0$ . En este caso,  $W_1$  es pequeña y es cercana a cero, por tanto de la ecuación (2.8) podemos sacar la tensión umbral de puerta:

$$V_T = \Phi_B - \Delta W_c - \frac{qN_D}{2\varepsilon} d_{Al}^2$$

(2.14)

Esta tensión puede ser positiva o negativa. Cuando es negativa estamos ante un HEMT de deplexión o empobrecimiento (DHEMT, depletion HEMT) y cuando es cero o positiva ante un HEMT de enriquecimiento (EHEMT, enhacement HEMT). Estos nombres son tomados del MESFET, aunque en el HEMT no son muy adecuados, ya que en este dispositivo tenemos ambos fenómenos: deplexión en el AlGaAs y enriquecimiento en el GaAs. Nosotros trabajaremos en el proyecto con un HEMT de empobrecimiento o deplexión, con tensión umbral de -0.9 V.

La corriente de drenador se puede obtener también, asumiendo la aproximación de velocidad de saturación:

$$I_D = q w_{ch} n_s v_{sat} (2.15)$$

La variación de la tensión de puerta en función del campo en la unión:

$$\Delta V_G = d_{Al} \Delta E_i \tag{2.16}$$

por tanto, la transconductancia se puede poner como:

$$g_{m} = \frac{\Delta I_{D}}{\Delta V_{G}} = \frac{w_{ch} \epsilon v_{sat}}{d_{Al}} = \frac{C_{G} v_{sat}}{L_{ch}}$$

(2.17)

Usando las ecuaciones (2.8) y (2.14):

$$I_D = \frac{W_{ch} \mathcal{E} V_{sat}}{d_{Al}} (V_G - V_T)$$

(2.18)

Según estas ecuaciones parecería que  $g_m$  cambia muy poco con la tensión de puerta, lo cual es una buena propiedad para muchas aplicaciones. Pero desafortunadamente, en la práctica las cosas no son así y  $g_m$  cambia, principalmente debido a dos efectos:

El canal no es infinitamente delgado, como hemos supuesto, sino que tiene un ancho no despreciable y, lo que es peor, no constante. En las ecuaciones de arriba habría que sustituir  $d_{Al}$  por  $d_{Al}+d_{ch}$ , donde  $d_{ch}$  es un ancho efectivo que caracteriza la dispersión espacial de los electrones en el canal. Cuando  $V_G$  se aproxima a  $V_T$ ,  $E_j$  decrece y el canal se ensancha. Consecuentemente la ecuación (2.16) se reemplazaría por:

$$\Delta V_G = (d_{Al} + d_{ch})\Delta E_i + E_i \Delta d_{ch}$$

(2.19)

- El potencia mínimo en el AlGaAs contendrá siempre algunos electrones y, aunque no influye en la corriente de DC del drenador, sí lo hace en la transconductancia. Las variaciones de la tensión de puerta no sólo modulará el canal principal, sino también el canal parásito, por lo que la modulación del primero se verá reducida. En particular, en el caso de tensiones de puerta positivas, cuando  $V_{\rm min}$  se hace pequeña esto tiene un fuerte efecto.

Lo que se obtiene finalmente es que la curva  $g_m$ - $V_G$  de un HEMT no es muy diferente de la de un MESFET, aunque es más ancha y su pico es más alto, principalmente debido a que la velocidad de canal es más alta y porque la capa de AlGaAs en un HEMT puede ser más delgada que la capa que contiene el canal de un MESFET.

#### 2.2.3. <u>Tecnología HEMT</u>

La cuestión ahora es cómo maximizar n<sub>s</sub>. El caso es que el HEMT de GaAs/AlGaAs se comporta de forma decepcionante en este aspecto, por la siguiente razón. Uno de los peores efectos que se producen en el AlGaAs es que los átomos de Si usados como donadores pueden formar los llamados *centros de recombinación o trampas*, los cuales tienen un nivel de energía próximo a la mitad de la zona prohibida. Esto produce fenómenos de relajación y ruido de baja frecuencia, así como también produce *fotoconductividad persistente*, lo cual significa que bajo iluminación se incrementa la conductividad, pero ésta se mantiene alta cuando cesa la iluminación. Este último efecto se produce a bajas temperaturas.

Para evitar estos problemas el contenido de Al debería mantenerse por debajo de un 25 %, lo cual significa que  $\Delta W_c$  no puede ser mayor a 0.23 V. El resultado es que la densidad superficial máxima que se puede obtener es de  $10^{12}/cm^3$ . Por tanto, el

HEMT de AlGaAs puede ser un dispositivo de alta transconductancia pero no un dispositivo de alta intensidad. Se comporta de forma excelente como un amplificador de pequeña señal y bajo ruido, pero no como amplificador de potencia. Por tanto, se puede decir que es un sustituto del MESFET como amplificador para frecuencias de más de 30 GHz.

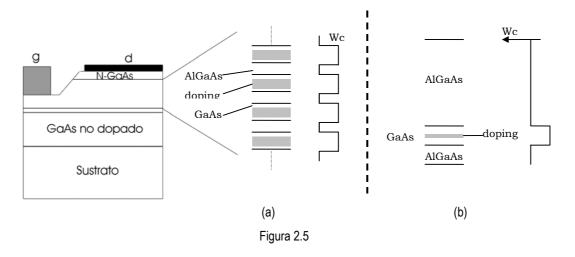

Se han pensado muchas soluciones para evitar los problemas con los centros de recombinación en los HEMT's. Todas intentan mantener los átomos de Si donadores lejos de los átomos de Al. Una solución consiste en reemplazar el AlGaAs por un enrejado de capas de AlAs y GaAs (de 5 nm de anchura cada una) de las cuales sólo éstas últimas están dopadas (figura 2.5(a)). Las barreras de AlAs son tan delgadas que los electrones pueden pasar fácilmente a través de ellas, y desde fuera el enrejado se ve como una única capa dopada de AlGaAs. Otro método consiste en poner una capa delgada (10 nm) de GaAs en la capa de AlGaAs cerca del canal. La capa de GaAs tiene a su vez una capa en el medio, muy delgada y fuertemente dopada. Esto es llamado *delta doping* (figura 2.5(b)).

Incluso con estos trucos la discontinuidad en la banda de conducción no puede ser aumentada demasiado debido a la estructura multivalle del GaAs. Si  $\Delta W_c$  se hace demasiado alta, los electrones del canal (los cuales aparecerán en el lado del drenador) pueden pasar al valle más alto donde su movilidad es baja. Por tanto, un valor de  $\Delta W_c$  de unos 0.3 V es lo máximo que se podría conseguir.

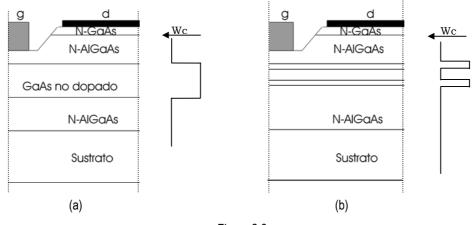

Para incrementar aún más la densidad transversal otra posibilidad es poner bajo la capa de GaAs un segunda capa de AlGaAs tipo n, de tal forma que se obtuviera un doble canal (figura 2.6(a)). Esto incrementa la conductividad del canal el doble. Una extensión de esta idea es un canal consistente en una estructura de pozo multicuántico (figura 2.6(b)). En este caso las barreras tienen que ser tan delgadas ( $\leq 3$  nm) que los electrones puedan pasar fácilmente a través de ellas; de otra forma, se obtendrían canales separados, lo cual daría lugar a fenómenos extraños, como una curva  $g_m\text{-}V_G$  con dos picos.

Como con la combinación AlGaAs/GaAs la discontinuidad en la banda no puede ser muy alta, en los últimos años se han buscado otras combinaciones para el canal, como In<sub>x</sub>Ga<sub>1-x</sub>As (usada en el proceso ED02AH de OMMIC). Este material tiene varias propiedades buenas: tiene una masa electrónica menor y una separación mayor entre los valles central y satélites que el GaAs. Esto último significa que cuando este material es usado en un HEMT, se puede conseguir una mayor discontinuidad en la banda de conducción.

Figura 2.6

El enrejado de  $In_xGa_{1-x}As$  no se ajusta con el GaAs, pero cuando x=0.53 sí se ajusta a InP, por tanto este material puede ser usado como sustrato. Como material de la zona más alta puede ser usado InP o mejor  $In_xAl_{1-x}As$ , que se ajusta al enrejado de InP, con x=0.48. Si, sin embargo, la capa de InGaAs no es demasiado ancha (<10 nm) y la cantidad de In no es demasiada alta, ésta puede ser intercalada entre dos capas de GaAs. Así, se extiende un poco la capa de InGaAs ( $strained\ layer$ , capa estirada o extendida). La combinación  $In_xGa_{1-x}As/AlGaAs$  con  $x \le 0.25$  puede ser depositada sobre sustratos de GaAs. Estos dispositivos son a menudo llamados InEMT's pseudomórficos (los que vamos a utilizar nosotros, del proceso InEMT).

Ambas combinaciones, InGaAs/InAlAs y InGaAs/AlGaAs, pueden proporcionar discontinuidades en la banda de conducción más altas. Consecuentemente se obtienen densidades transversales más altas:  $2x10^{12}/cm^2$  para InGaAs/AlGaAs y  $3x10^{12}/cm^2$  para InGaAs/InAlAs. El transistor puede alcanzar prestaciones muy buenas: valores de  $g_m$  de 500 mS/mm y 1000mS/mm y frecuencias de corte de 110 GHz y 170 GHz para InGaAs/AlGaAs y InGaAs/InAlAs, respectivamente.

#### 2.2.4. Ruido en el HEMT

El modelo más simple de ruido, dado por Fukui, asume que la fuente principal de ruido en un MESFET y un HEMT es el ruido térmico de las resistencias de puerta y fuente. Esto conduce a la siguiente fórmula de la mínima figura de ruido:

$$F_{min} = 1 + k_1 C_G s f \left(\frac{Rs + R_G}{g_m}\right)^{1/2} = 1 + K_F \frac{f}{f_T} \left[g_m (Rs + R_G)\right]^{1/2}$$

(2.20)

donde  $k_1$  es un factor de ajuste, y cuyo valor depende del transistor en estudio. Por ejemplo, Fukui le dio para el MESFET el valor 0.016; para el HEMT su valor es menor.  $K_F$  es llamado factor Fukui y es igual a  $k_1/2\pi$ .

#### 2.3. PROCESO ED02AH DE OMMIC ([3])

El proceso ED02AH de OMMIC fue desarrollado específicamente para aplicaciones de microondas hasta la banda de ondas milimétricas, y para circuitos digitales de alto régimen binario en enlaces de fibra óptica. El significado de las siglas es el siguiente:

- E: Transistor de enriquecimiento.

- D: Transistor de deplexión.

- 02: Longitud de puerta de 0.2 μm (en realidad, 0.18 μm).

- A: Proceso OMMIC tipo A.

- H: HEMT con capa pseudomórfica.

Las principales características de esta tecnología se resumen a continuación:

- Capa activa pseudomórfica de GaInAs.

- Transistores de deplexión y enriquecimiento: Vt=0.225 V o -0.9 V.

- Dos tipos de diodos (0.18  $\mu m$  con capa "GM" y 3  $\mu m$  con capa "BE") para mezcladores, varactores o desplazadores de nivel.

- Resistencias con capa activa de GaAs.

- Resistencias con capa metálica fina de NiCr.

- Protección completa con Si<sub>3</sub>N<sub>4</sub>, que asegura gran fiabilidad.

- Dos tipos de capacidades MIM, una con capa de  $Si_3N_4$  y la otra con capa de  $Si_3N_4$ + $SiO_2$ .

- $Si_3N_4/SiO_2$  + aislamiento con puente de aire entre las capas para reducir las capacidades parásitas.

- Metalización gruesa de oro de  $1.25~\mu m$  para interconexiones e inductancias en espiral. Es posible la utilización de multilíneas metálicas para reducir las resistencias parásitas en serie.

- Conexiones a tierra (*via holes*) a través de sustratos de 100 μm de espesor para reducir las inductancias parásitas a tierra.

- Para circuitos digitales tales como multiplexores o demultiplexores de 40 Gbps, se dispone de transistores con longitud de puerta de 0.13 μm en lugar de 0.18 μm (proceso ED01AH). Esto incrementa la frecuencia máxima a 75 GHz o más. En este caso sería necesario introducir en los modelos como parámetro la longitud de puerta.

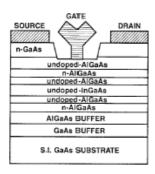

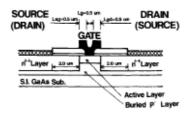

Los componentes activos están basados en una heteroestructura (Ga,Al)As - (Ga,In)As – GaAs obtenida mediante MOVPE, usando un sistema industrial multioblea. El perfil de la capa activa del proceso ED02AH se muestra abajo:

Figura 2.7

La relación de capas que se usan en el proceso ED02AH es la siguiente:

- 1. **Aislamiento (Máscara LI)**. El aislamiento entre los componentes activos (pHEMT's, diodos, resistencias) se logra con una aplicación de boro en las zonas requeridas, mientras que una capa metálica protege las zonas activas delimitadas por la máscara LI.

- 2. **Contactos óhmicos (Máscara OH)**. Consistente en un capa de AuGeNi, y, como es obvio, se deposita en las regiones de contacto.

- 3. **Depósito de metal para resistencia NiCr (Máscara MD).** Sólo disponible si se opta por resistencias de NiCr. Se trata de depositar una fina capa de NiCr de 40  $\Omega$ \*cuadrado en el sustrato para obtener resistencias de alta precisión.

- 4. Electrodo inferior de la capacidad MIM y para diodos de 3 μm (Máscara BE). Es usada para el electrodo inferior de las capacidades MIM, como primera capa metálica para interconexión, por ejemplo, en líneas de transmisión, y para los diodos de 3 μm. El grosor total del metal BE es 650 nm.

- 5. Hueco del canal y metalización de la puerta (Máscaras LE y GM). Las puertas de longitud 0.18 μm se realizan con un equipo de haz de electrones. Primero se hace el hueco del canal y después se deposita el metal de la puerta. La anchura total de la puerta es 360 nm.

- 6. **Deposición de Si<sub>3</sub>N<sub>4</sub>.** Una capa de Si<sub>3</sub>N<sub>4</sub> de 150 nm es depositada en la oblea para proteger las zonas activas y formar el dieléctrico para las capacidades MIM. Si<sub>3</sub>N<sub>4</sub> es usado debido a su alta constante diélectrica, adecuado para las capacidades MIM, y para prevenir la formación de óxidos de As y Ga inestables en la superficie de la oblea.

- **7.** Ataque con ácido de la capa de Si<sub>3</sub>N<sub>4</sub> (Máscara CG). Se abren vías a través de la capa Si<sub>3</sub>N<sub>4</sub> con la máscara CG para habilitar el contacto (pads) con los metales previamente depositados.

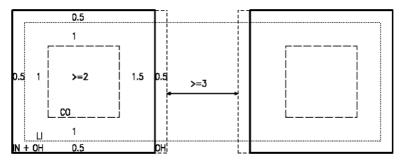

- 8. Electrodos superiores de la capacidad MIM (Máscara TE). Un metal es evaporado y delimitado para formar los electrodos superiores de las capacidades MIM. Esta capacidad es también usada como una protección entre las puertas de TiAl y las líneas de Au para una alta fiabilidad y como una capa de contacto para las resistencias NiCr.

- **9. Deposición de dieléctrico y abertura de contacto (Máscara CO).** Se deposita un óxido de Si de 800 nm de anchura en la oblea. Se abren ventanas para interconectar la segunda metalización con los metales OH, BE y TE.

- 10. Puentes de aire (Máscara AB). Se deposita un pad fotoresistivo de 1  $\mu$ m de grosor. Después de la evaporación de la segunda metalización, se quita este pad dejando un puente de aire de 1  $\mu$ m.

- **11. Segunda metalización (Máscara IN).** Se evapora una capa de TiPtAu de 1.25 μm de grosor. Después se delimita la capa de segunda metalización.

- **12. Protección final.** Se deposita una segunda capa de Si<sub>3</sub>N<sub>4</sub> de 150 nm de grosor. La técnica PECVD asegura el total encapsulado del circuito.

- **13. Abertura de** *pads* **(Máscara CB).** Las zonas de contacto son abiertas para las entradas y salidas del circuito.

#### 2.3.1. Componentes utilizados

En este apartado se va a explicar algunos componentes de la librería de la *Foundry* que se van a usar para la realización del diseño del conmutador. No se va a entrar en mucho detalle, pero sí en los aspectos más importantes. Quizá no se utilicen todos ellos, pero es bueno sentar unas bases para ellos.

#### 2.3.1.1. Transistor de empobrecimiento

Aunque la *Foundry* dispone también de transistor de enriquecimiento, nosotros lo dejaremos un poco de lado, pues no es utilizado en nuestro proyecto.

En cuanto al transistor de empobrecimiento o deplexión, su tensión umbral es -0.9~V y, al igual que el transistor de enriquecimiento, tiene una estructura multidedo. Con esta estructura se consigue tener un ancho de puerta importante, lo cual es necesario para tener una potencia de salida grande. Si no se tuviese esta estructura, se podría aumentar el ancho de puerta igualmente, pero redundaría en un aumento de la resistencia de puerta y por tanto una menor ganancia disponible y un mayor ruido. Así, el tamaño de los transistores se especifican como Nbd x  $W_u$ , con Nbd el número de dedos y  $W_u$  la anchura de puerta por cada dedo.

#### a) Características DC

| Nombre | Definición                                                                                                  | Unidad | Escalado | Valor |

|--------|-------------------------------------------------------------------------------------------------------------|--------|----------|-------|

| Vt     | Tensión umbral: V <sub>gs</sub> para<br>I <sub>ds</sub> =1mA/mm y Vds=3 V                                   | V      | 1        | -0.9  |

| Idss   | Intensidad drenador-fuente de<br>saturación para V <sub>gs</sub> =0 Vy V <sub>ds</sub> =3 V                 | mA/mm  | x W      | 250   |

| Vbrgss | Tensión (drenador+fuente) – puerta<br>para I <sub>g</sub> =1 ma/mm (drenador y fuente<br>cortocircuitados)  | V      | -        | -0.8  |

| Vleak  | Tensión (drenador+fuente) – puerta<br>para I <sub>g</sub> =10 μa/mm (drenador y fuente<br>cortocircuitados) | V      | -        | -4.6  |

| Gm     | Transconductancia DC para $V_{gs}$ =0 V $y V_{ds}$ =3 V                                                     | mS/mm  | x W      | 440   |

Tabla 2.2

Se puede observar que el valor de la transconductancia concuerda con el predicho teóricamente en el apartado anterior, en el que se hablaba de un valor de  $500~\rm mS/mm$ .

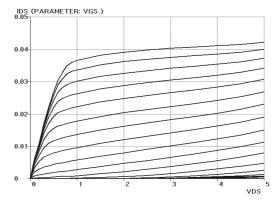

Figura 2.8

En la figura antenrior se muestra la curva  $I_{ds}(V_{ds})$  para un transistor de empobrecimiento de tamaño 6 x 15, con  $V_{gs}$  como parámetro, y con  $V_{gs}(máx)$ =+0.6 V y  $V_{gs}(step)$ =+0.1 V.

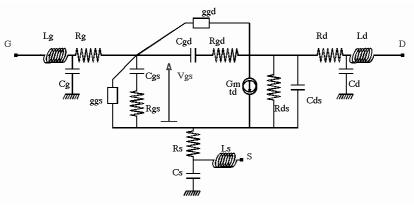

#### b) Modelo de pequeña señal

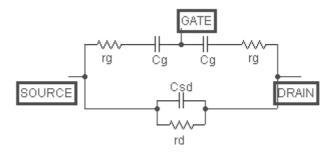

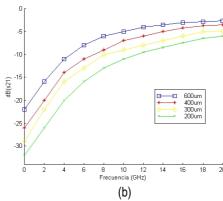

Los parámetros RF del transistor se dan según un circuito equivalente que depende de la polarización y la geometría. El circuito equivalente de pequeña señal propuesto por la *Foundry* se muestra en la figura 2.9.

Figura 2.9

Los parámetros del modelo son:

- W: anchura total de la puerta.

- Nbd: número de dedos de la puerta.

- W<sub>u</sub>: anchura unitaria de la puerta (=W/Nbd).

- V<sub>gs</sub>: Tensión puerta-fuente de polarización.

- V<sub>ds</sub>: Tensión drenador-fuente de polarización.

Los elementos del circuito equivalente que se muestra arriba tienen el significado:

- C<sub>g</sub>, C<sub>d</sub>, C<sub>s</sub>, L<sub>g</sub>, L<sub>d</sub>, L<sub>s</sub> son parásitos externos del transistor.

- R<sub>g</sub> ,R<sub>s</sub> ,R<sub>d</sub> son las resistencias de acceso del transistor.

- $C_{gs}$ ,  $C_{gd}$ ,  $C_{ds}$ ,  $R_{ds}$ ,  $R_{gs}$ ,  $g_m$  y  $t_d$  son los elementos del circuito equivalente de un pHEMT de GaAs clásico.

- $G_{gd}$  (conductancia puerta-drenador,  $G_{gs}$  (conductancia puerta-fuente) y  $R_{gd}$  (resistencia serie drenador-puerta) son elementos adicionales útiles para una mejor precisión en las siguientes condiciones:

- $G_{gd}(mS)$  cuando el diodo puerta-drenador está polarizado de forma directa ( $V_{gd}$ >>0.2 V) o polarizado fuertemente de forma inversa ( $V_{gd}$ << $V_t$ ).

- $G_{gs}$  (mS) cuando el diodo puerta-fuente está polarizado de forma directa ( $V_{gs}$ >>+0.2 V) o polarizado fuertemente de forma inversa ( $V_{gs}$ << $V_t$ ).

- $R_{gd}$  (Ohms) es usada principalmente para tener un modelo simétrico en la zona óhmica ( $V_{ds}$ <1.5 V).

Fuera de los supuestos anteriores,  $G_{gd}$ ,  $G_{gs}$  y  $R_{gd}$  pueden ser despreciadas por simplicidad.

Como se ha comentado anteriormente, la anchura de puerta unitaria es W/Nbd. Aunque puede tomar valores de hasta 300 o 400  $\mu$ m, se recomienda, excepto para el diseño de circuitos como switches o amplificadores de potencia de baja frecuencia, que no sobrepase los 50  $\mu$ m para que la resistencia serie no sea muy grande y así tener una mayor ganancia disponible.

El manual de diseño de la *Foundry* proporciona un fichero con los valores escalados de los elementos del circuito equivalente. Con la anchura total de puerta W y el número de dedos Nbd podemos calcular los valores totales de dichos elementos siguiendo las reglas de escalado, mostradas abajo.

$$Rg = Rg_0 \times W / Nbd^2$$

$$Rs = Rs_0 / W$$

$$Rd = Rd_0 / W$$

$$Cgs = Cgs_0 \times W + Nbd \times Cgse$$

$$gm = gm_0 \times W$$

$$Cgd = Cgd_0 \times W + Nbd \times Cgde$$

$$ggs = ggs_0 \times W$$

$$Cds = Cds_0 \times W + Nbd \times Cdse$$

$$ggd = ggd_0 \times W$$

$$td = td_0$$

$$Rgs = Rgs_0 / W$$

$$Rgd = Rgd_0 / W$$

$$Rds = Rds_0 / W$$

Figura 2.10

Para calcular el valor de los demás elementos y parámetros hay unas ecuaciones que proporciona el manual de diseño. Las reglas de escalado mostradas arriba serán utilizadas para los cálculos teóricos previos al diseño de los switches. Para terminar, sólo apuntar que las reglas de escalado de arriba son válidas para valores  $Nbd \leq 10$  y  $W \leq 50$   $\mu m$ .

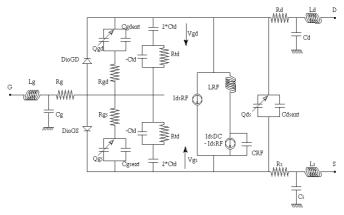

#### c) Modelo no lineal

Para el diseño de circuitos en simuladores no lineales, OMMIC propone un modelo avanzado no lineal para describir las no linealidades existentes en la corriente y la capacitancia de los transistores. Este modelo da muy buenos resultados, en particular representa mucho mejor  $G_m$ ,  $G_d$  y las variaciones de carga que la mayoría de los modelos que se usan normalmente en los simuladores. Puede ser implementado en un simulador no lineal que permita al usuario definir ecuaciones y modelos (ADS, algunas versiones de SPICE). En la figura 2.11 se muestra la estructura del modelo no lineal de OMMIC.

Se puede observar que, a diferencia del circuito equivalente de pequeña señal, se incluyen unos diodos, que se encargan de modelar las pequeñas corrientes que circulan entre puerta y drenador y entre puerta y fuente. Dichas corrientes son despreciables en un punto de funcionamiento normal del circuito, y sólo se tienen en cuenta en caso de que las tensiones externas alcancen un valor particularmente elevado.

Figura 2.11

Otro elemento interesante que aporta el modelo no lineal es la red RC formada por el paralelo entre – $C_{td}$  y  $R_{td}$  más la capacidad en serie  $2C_{td}$ . Esta red se encarga de modelar el efecto del retraso de puerta mediante la transformación de la tensión  $V_{gs}$  en otra tensión  $V_{delay}$ , que se mide en los terminales de la capacidad  $2C_{td}$ , en la que se basan las expresiones del modelo.

Los parámetros de entrada del modelo no lineal se muestran en la siguiente tabla.

| Nombre                    | Descripción                                                                                               | Valor por defecto |

|---------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|

| Nbd                       | Número de dedos de la puerta                                                                              | 6                 |

| $\mathbf{W}_{\mathrm{u}}$ | Anchura unitaria de la puerta                                                                             | 15 μm             |

| Vtpcm                     | Parámetro de sensibilidad para simular dispositivos con diferente Vt                                      | -0.9 V            |

| Kidss                     | Parámetro de sensibilidad para simular<br>dispositivos con diferentes valores de Idss para<br>una Vt dado | 1                 |

| Lgate0                    | Parámetro de sensibilidad para simular dispositivos con diferentes longitudes de puerta                   | 0.2 μm            |

| Vbrgss                    | Parámetro de sensibilidad para simular dispositivos con diferentes tensiones de ruptura                   | -8 V              |

| Rth                       | Resistencia térmica para cálculos de calor propio                                                         | 0 °C/Watt         |

| Vdsbias                   | Punto de trabajo de DC del dispositivo para<br>cálculos de calor propio                                   | 0 V               |

| Idsbias                   | Punto de trabajo de DC del dispositivo para<br>cálculos de calor propio                                   | 0 A               |

Tabla 2.3

Los elementos de acceso y parásitos son los mismos que los del modelo de pequeña señal. Sin embargo, las variaciones de  $R_{\rm gs0},\,R_{\rm gd0}\,y\,t_{\rm d0}$  con  $V_{\rm gs}\,y\,V_{\rm ds}$  son despreciadas para disminuir la complejidad del modelo.

En cuanto a los elementos no lineales del modelo, hay básicamente tres:

- Las corrientes drenador-fuente, tanto la de DC como la de RF.

- Las cargas puerta-drenador, puerta-fuente y fuente-drenador.

- Las corrientes de los diodos puerta-drenador y puerta-fuente.

Esto es sólo un pequeño resumen del modelo no lineal del transistor; para una mayor profundización en el tema, se remite al lector al manual de diseño de la *Foundry*.

#### 2.3.1.2. Capacidades

La Foundry presenta dos tipos de capacidades:

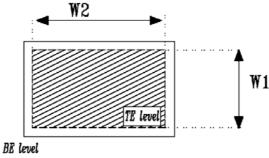

- Capacidades SiN. Son fabricadas usando una capa de SiN de 150 nm entre las capas BE (primera metalización) y TE (electrodo superior). Sus dimensiones mínimas son 10 μm x 10 μm, que se corresponde con un valor de 0.06 pF. Como valor máximo puede alcanzar 50 pF. Para una mayor precisión se aconseja que 1/3 ≤ W1/W2 ≤ 3. En el manual de diseño se puede calcular el valor de la capacidad según unas dimensiones y viceversa, algo muy útil para la posterior implementación del *layout*. Su aspecto es el que se muestra abajo:

Figura 2.12

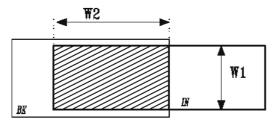

Capacidades SiN + SiO<sub>2</sub>. Son fabricadas usando una capa de SiN + SiO<sub>2</sub> de 150 nm entre la primera metalización (BE) y la segunda metalización (IN). Su aspecto se muestra abajo:

Figura 2.13

Sus dimensiones mínimas son 10  $\mu$ m x 10  $\mu$ m, que se corresponde con un valor de unos 69 fF. Como valor máximo puede alcanzar 1 pF. Al igual que la capacidad anterior, se pueden calcular las dimensiones de la capacidad por su valor y viceversa.

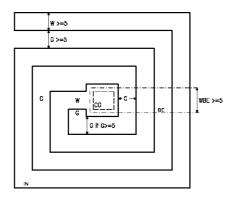

#### 2.3.1.3. Inductancias de espiral

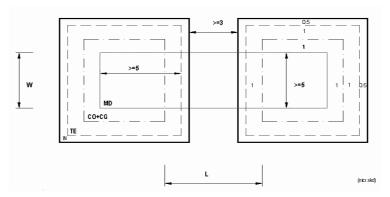

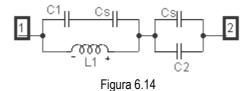

Son fabricadas con una banda de oro de 1.25 µm definida por la máscara IN. La banda de retorno se hace con la primera metalización (capa BE). Su aspecto se muestra en la figura 2.14. Se puede observar las limitaciones en relación a la anchura

Figura 2.14

de las bandas y su separación. El manual de diseño proporciona la posibilidad de calcular su tamaño. En este elemento es muy importante este aspecto, ya que se trata del componente de mayor tamaño. Su valor máximo es 15 nH.

#### 2.3.1.4. Resistencias

Hay dos tipos de resistencias:

- Resistencias de GaAs. Son fabricadas usando la capa activa (ver figura 2.7). La longitud de la resistencia es definida por la distancia entre los dos contactos óhmicos (máscara OH), y el ancho (W) de la resistencia lo da el ancho de la capa activa (máscara LI). Como el GaAs exhibe una movilidad electrónica que depende del campo, hay que tener cuidado en el dimensionamiento de las resistencias para evitar saturación en la intensidad: una resistencia puede ser considerada lineal por debajo de Vlin=0.075 V/μm de longitud. Su aspecto y limitaciones en cuanto a dimensiones se muestran abajo:

Figura 2.15

- Resistencias de NiCr. Para resistencias de valores pequeños o de alta precisión, se proporciona una resistencia de NiCr de lámina delgada, de 40 Ohms.cuadrado.

Figura 2.16

La longitud de la resistencia (L) es definida por la distancia entre los dos bordes internos de la máscara CG, y el ancho (W) es dado por el ancho de la capa resistiva (máscara MD). Hay que tener cuidado en el *layout* de hacer las resistencias lo suficientemente anchas como para soportar la corriente de DC: la máxima corriente permitida para conseguir una gran fiabilidad es de 0.2 mA/µm de ancho, y la ruptura ocurre antes de 4 mA/µm de ancho.

En este apartado se han explicado algunos de los elementos de la *Foundry* más importantes que se van a usar; por supuesto, quedan muchos por nombrar, y no menos importantes, como las líneas de transmisión, las conexiones a tierra, etc. Para más información sobre estos elementos, así como los reseñados anteriormente, se remite al lector al manual de diseño de la *Foundry*.

# 3. <u>RESEÑA TEÓRICA DE SWITCHES</u>

## 3.1. CONFIGURACIÓN Y FUNCIONAMIENTO BÁSICOS ([4])

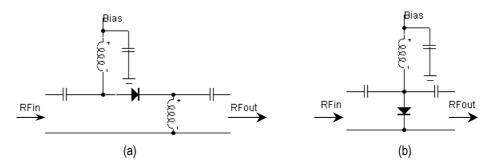

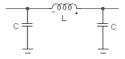

Para las configuraciones de conmutador que se van a explicar a continuación se puede usar tanto diodos PIN como FET's. Sin embargo, por simplicidad se usará el símbolo del diodo para representar ambos. En la figura 3.1 se muestran dos implementaciones de conmutador SPST (Single-Pole Single-Throw). Para la topología en serie (figura 3.1(a)), el conmutador están en conducción cuando el diodo está en su estado de baja resistencia y en otro caso está en corte. En cambio, para la topología en paralelo (figura 3.1(b)) el funcionamiento es el inverso. Las capacidades e inductancias son necesarias para proporcionar una adecuada alimentación a cada diodo y para evitar la salida de potencia de RF a través del puerto de alimentación. Para la configuración en serie, las pérdidas de inserción y las pérdidas por retorno tienen unas expresiones:

$$IL = -10\log |S_{21}|^2 = 20\log \left| \frac{2 + Y_d / Y_o}{2} \right|$$

(3.1)

$$RL = 10\log \left| S_{11} \right|^2 = 20\log \left| \frac{Y_d / Y_o}{2 + Y_d / Y_o} \right|$$

(3.2)

Donde  $Z_d$  es la impedancia del diodo (o del FET), y  $Z_o$  es la impedancia característica de las líneas de transmisión de entrada y salida. Similarmente, para la configuración en paralelo:

$$IL = -10\log |S_{21}|^2 = 20\log \frac{2 + Y_d / Y_o}{2}$$

(3.3)

$$RL = 10\log \left| S_{11} \right|^2 = 20\log \left| \frac{Y_d / Y_o}{2 + Y_d / Y_o} \right|$$

(3.4)

Donde  $Y_d=1/Z_d$  y  $Y_o=1/Z_o$ .

Figura 3.1

Normalmente es interesante observar las pérdidas de inserción cuando el dispositivo está en conducción y la diferencia entre los valores de pérdidas de inserción para los dos estados, donde las pérdidas de inserción para el estado de corte son llamadas aislamiento. El diseño o selección de un diodo PIN o un FET para un conmutador requiere hacer una serie de *trade-offs* entre la resistencia de conducción y la capacidad de corte. La elección influye directamente en la relación conducción/corte para el conmutador.

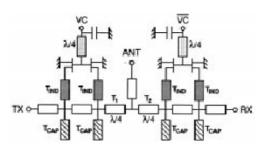

Los circuitos mostrados anteriormente son reflexivos en el estado de corte, lo cual podría ser indeseable. Esta situación puede ser remediada poniendo dos diodos en configuración SPDT (Single-Pole Double-Throw), como ilustra la figura 3.2(a) de abajo y terminando uno de los dos puertos de salida con una carga adaptada. Un conmutador SPDT que usa sólo diodos en paralelo es mostrado en la figura 3.2(b). Las líneas de transmisión son requeridas en este caso para proporcionar la adecuada acción de conmutación.

Figura 3.2

Cuando el diodo A está en conducción se puede asemejar como una baja resistencia a tierra, por lo que no pasará señal hacia el puerto 1; además, en el punto de unión común se ve como un circuito abierto, debido a la línea de lambda/4, por lo que ese brazo del circuito no afectaría al brazo de recepción. En cambio, cuando el diodo A está en corte (alta resistencia), se dejará pasar señal hacia el puerto 1; además, en el punto de unión común se ve como un circuito abierto y este brazo no influiría en este caso en el brazo de recepción. Si los diodos A y B están complementariamente alimentados de forma adecuada, la conmutación se producirá de forma correcta. La introducción de líneas de transmisión tiende a reducir el ancho de banda útil a menos de una octava.

Incrementando el número de diodos (o FET's) usados, se pueden extender estos diseños simples para realizar conmutadores con un mayor número de polos y caminos.

#### 3.2. SWITCHES MMIC CON FET'S DE GAAS ([1])

La implementación de switches con diodos PIN hace varias décadas resultó un mejora significativa en el manejo, tamaño y velocidad de conmutación de los switches de microondas, comparados con sus homólogos electromecánicos de entonces. Tales circuitos con diodos PIN pueden ser fácilmente realizados en circuitos integrados híbridos. Esto posibilitó su amplio uso en numerosas aplicaciones. Los diodos PIN pueden proporcionar velocidades de conmutación más rápidas y pueden manejar potencias de RF de medio y alto nivel. Los requerimientos de polarización de los diodos PIN son tales que en el estado de conducción requieren una alta intensidad directa y en el estado de corte requieren una gran polarización inversa a través de la unión semiconductora. Las características de conmutación de estos switches son altamente dependientes de las características individuales del diodo PIN. Hace pocos años estos switches han ido siendo reemplazados por los switches monolíticos basados en FET's de GaAs, especialmente para aplicaciones de baja potencia.

Las ventajas inherentes de los switches basados en FET's de GaAs sobre los convencionales basados en diodos PIN son: redes de polarización más simples, requerimientos de potencia de DC despreciables, velocidades de conmutación más rápidas, etc. Además, la implementación monolítica de tales switches resulta en circuitos con muy altas prestaciones y en chips muy pequeños.

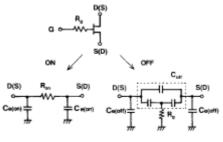

#### 3.2.1. Mecanismo de conmutación de un FET de GaAs

El FET como conmutador es un dispositivo de tres terminales en el que la tensión de puerta controla los estados del transistor. El FET se comporta como una resistencia controlada por tensión en la cual la tensión de puerta controla la resistencia drenador-fuente en el canal. Las capacitancias intrínsecas puerta-fuente y drenador-puerta y los parásitos del dispositivo limitan el rendimiento del FET como conmutador a altas frecuencias.

En un típico modo de conmutación, el estado de alta impedancia se alcanza cuando una polarización negativa, mayor en magnitud a la tensión de *pinchoff* del transistor ( $|V_g| > |V_p|$ ), es aplicada a través del terminal de puerta. Cuando la tensión de puerta es cero, el FET estará en un estado de baja impedancia. Es importante hacer notar que, en ambos estados de polarización, el FET no requiere potencia de DC (idealmente), por lo que, desde el punto de vista del consumo de potencia, estos elementos pueden ser considerados dispositivos pasivos. Este hecho hace que los FET's tengan una circuitería de alimentación muy sencilla. Siendo una estructura plana, con la banda de puerta localizada entre los terminales de drenador y fuente el FET se comporta como un switch bidireccional.

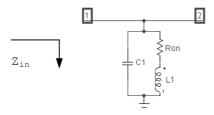

El FET puede ser modelado por combinaciones serie y paralelo de resistencias y capacidades.

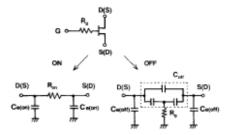

Figura 3.3

Asumiendo que la terminación de puerta presenta una impedancia muy grande para nuestra frecuencia de operación, el circuito equivalente en estado de corte puede ser algo como el mostrado en la figura 3.3. Para condiciones de  $1/\omega C_g >> r_g$ , la capacidad efectiva drenador-fuente es simplemente ( $C_{sd} + C_g/2$ ) y la resistencia efectiva del drenador es el paralelo entre  $r_d$  y  $2/(\omega^2 C_g^2 r_g)$ . La figura de mérito de un FET puede ser expresada como la relación entre su resistencia efectiva en estado de corte y su resistencia en estado de conducción.

Los parámetros físicos del dispositivo influyen fuertemente en los parámetros del circuito equivalente del FET. Los parámetros físicos más importantes son: la geometría del canal, la longitud de puerta, el grado de dopado del canal y la tensión de *pinchoff.* La metalización, el hueco de puerta, etc., influyen en la resistencia de conducción del FET; la impedancia de corte depende de la capacidad fuente-drenador  $(C_{sd})$ , su resistencia paralelo  $(r_d)$ , y las capacidades drenador-puerta y fuente-puerta  $(C_g)$ , con sus respectivas resistencias serie  $(r_g)$ .

El valor de la capacidad  $C_{sd}$  depende del espacio entre los terminales de fuente y drenador, y es idealmente independiente de los parámetros del dispositivo como el dopado del canal y la tensión de *pinchoff*. Debido a la simetría del dispositivo, las capacidades drenador-puerta y puerta-fuente son iguales y representadas por  $C_g$ . La capacidad de puerta a tierra, si es significativa, debe ser añadida al modelo. Las resistencias que contribuyen a la impedancia de corte son  $r_d$  y  $r_g$ . La resistencia  $r_d$  está en paralelo con  $C_{sd}$  y representa las pérdidas de RF asociadas a la capacidad fuente-drenador. La resistencia  $r_g$  representa la resistencia del canal fuera de la región de *pinchoff* en la condición de corte.

La velocidad de conmutación de un FET también puede ser calculada mediante los parámetros del circuito equivalente. Asumiendo una resistencia interna de puerta de  $1.5~\mathrm{k}\Omega$  y que para el filtro pasobajo del circuito de polarización se ha utilizado una capacidad de  $10~\mathrm{pF}$ , el tiempo de carga será de  $15~\mathrm{ns}$ . La reducción de los tiempos de conmutación son posibles optimizando el diseño del circuito de polarización de la puerta.

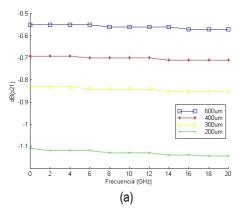

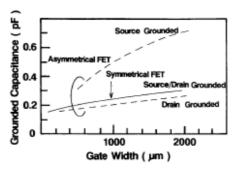

#### 3.2.2. Circuito equivalente del FET como conmutador

En la figura 3.4(a) se muestran las pérdidas de inserción para un FET serie de cuatro dedos, en conducción, en función de la periferia total de puerta. Como era de esperar, las pérdidas de inserción decrecen conforme aumenta la periferia total de puerta. En la figura 3.4(b) se muestran las pérdidas de inserción para el mismo FET en corte. Debido al incremento del acoplamiento capacitivo, el aislamiento en el estado de corte más bajo para dispositivos con una periferia de puerta mayor que para dispositivos con periferia de puerta menor. Las características de conmutación están dadas principalmente por la anchura total de puerta; el número de dedos tiene una influencia mucho menor.

Figura 3.4

En el estado de conducción la resistencia de canal del FET es el parámetro dominante y esto resulta en que las pérdidas de inserción son idealmente independientes de la frecuencia. En el estado de corte, sin embargo, la capacidad equivalente del circuito determina la característica de aislamiento, la cual muestra una fuerte dependencia con la frecuencia. Por lo tanto, las pérdidas de inserción para el FET serie y el aislamiento para la configuración en paralelo muestran un comportamiento invariable con la frecuencia. Por otra parte, el aislamiento para el FET serie y las pérdidas de inserción para el FET paralelo muestran una dependencia con la frecuencia debido a efectos capacitivos en el estado de corte. Incrementando el tamaño del FET se reduce su resistencia de conducción y entonces reduce las pérdidas de inserción. Sin embargo, esto también resulta en un incremento de las capacidades puerta-fuente y puerta-drenador, y también de la capacidad fuente-drenador, que es la que limita el rendimiento del switch en el estado de corte.

#### 3.2.3. Implementación de switches MMIC

Los circuitos de conmutación con FET's pueden ser diseñados de la misma forma que los realizados con diodos PIN mediante el uso de circuitos equivalentes de estado de corte y conducción. El FET puede estar en configuración serie o paralelo con respecto a las líneas de transmisión a las cuales se conectan. Es importante hacer notar las diferencias entre los switches basados en diodos PIN respecto a los switches MMIC basados en FET's. Como el FET es un dispositivo de tres terminales, la conmutación se produce sólo mediante la tensión de control en la puerta; ninguna otra tensión es necesaria para el funcionamiento del switch. Las líneas de transmisión de RF no llevan ninguna tensión DC y por lo tanto no hay necesidad de usar capacidades DC de bloqueo entre los distintos elementos de conmutación. Esto representa una ventaja muy significativa, ya que resulta una configuración más simple para los circuitos MMIC.

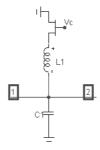

En los estados del switch la unión de puerta está o polarizada inversamente o polarizada directamente mediante una tensión de puerta igual a cero. En ambos estados la corriente de puerta es despreciable, lo cual simplifica de forma importante el circuito de control. En el estado de corte del switch con FET, las capacidades puerta-drenador y puerta-fuente son iguales; en este caso resulta que los terminales de puerta y drenador no están aislados el uno del otro y la impedancia de RF del circuito de polarización de la puerta afecta a la impedancia equivalente drenadorfuente. Cuando la impedancia de puerta es muy alta la capacidad drenador-fuente equivalente puede tomar un valor aproximado de  $C_d+C_g/2$ . El efecto de esta capacidad debería ser incluida en el diseño de los circuitos en estado de corte. Para frecuencias en la banda X o superiores este efecto capacitivo paralelo en el estado de corte podría ocasionar que la impedancia de corte del FET fuese mucho menor que el valor de  $r_d$ . Podría ser necesario poner una inductancia entre el drenador y la fuente para que, junto a esa capacidad, resonaran a la frecuencia de interés.

Las características de switches simples monolíticos con FET's mostradas en las figuras 3.4(a) y 3.4(b) pueden ser adecuadas para ciertas aplicaciones, pero generalmente es necesario una combinación de configuraciones serie-paralelo para conseguir las características deseadas, tales como bajas pérdidas de inserción y alto aislamiento.

## 3.3. <u>DIFERENTES</u> <u>CONFIGURACIONES</u> <u>DE</u> <u>SWITCHES</u> CON FET'S

En este apartado se pretenden mostrar distintos conmutadores de antena propuestos en diversos artículos, y completar así el desarrollo teórico visto previamente.

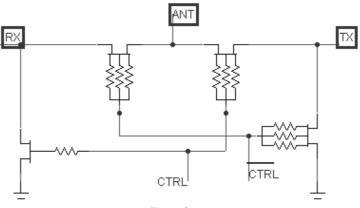

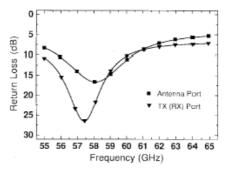

#### 3.3.1. Switch T/R para comunicaciones personales a 1.9 GHz

Este apartado está basado en el artículo "High Performance Integrated PA, T/R Switch for 1.9 GHz Personal Communications Handsets" ([5]). Como se dice en el título se trata de un circuito que integra un amplificador de potencia y un conmutador de antena, pero nosotros nos centraremos en este último.

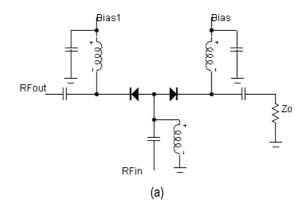

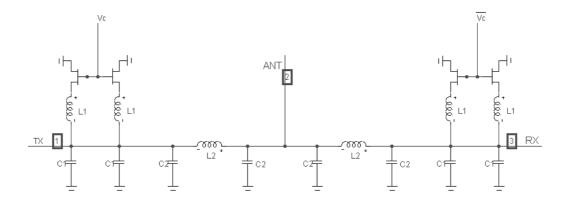

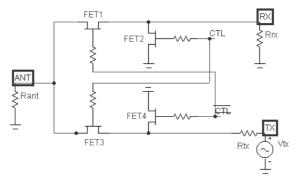

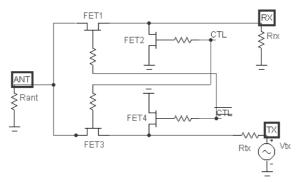

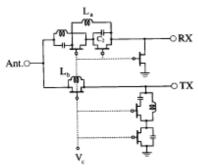

El circuito se realiza en tecnología MMIC, y se usan MESFET's de GaAs multipuerta. Los requerimientos de intermodulación que se le exigen a este switch están muy por encima de los que se les pide a los switches convencionales que usan FET's de GaAs. Para superar este problema, se usa esta configuración multipuerta para los transistores, ya que permite reducir la tensión AC que aparece entre la puerta y el drenador o fuente, lográndose así que el switch pueda manejar potencias más altas. El circuito se muestra en la siguiente figura:

Figura 3.5

La resistencia de conducción del FET multipuerta es cerca de 2.5 veces mayor que la de un FET de una puerta de la misma periferia. Para compensar esto se deben usar FET's más grandes. Como en un FET multipuerta la distancia entre drenador y fuente es mayor que para un FET de una puerta, la capacidad equivalente en estado de corte es menor que para un FET de una sola puerta. La consiguiente pérdida de aislamiento que se produce al aumentar el tamaño de los transistores, necesario para disminuir las pérdidas de inserción, es muy pequeña. El FET en paralelo del brazo de recepción puede ser de una puerta, sin que esto afecte a la linealidad del circuito. Este diseño asimétrico permite adaptarse a las necesidades de los dos modos de funcionamiento. La periferia o tamaño de los FET's se optimiza para conseguir que su capacidad de corte junto a las inductancias series parásitas del chip resuenen a la frecuencia deseada. En la tabla siguiente se muestran los resultados obtenidos:

| Pérdidas de inserción | <1 dB  |

|-----------------------|--------|

| Aislamiento           | 30dB   |

| Tensiones de control  | 0/-4 V |

| IP3out (Pin=23 dBm)   | 48 dBm |

Tabla 3.1

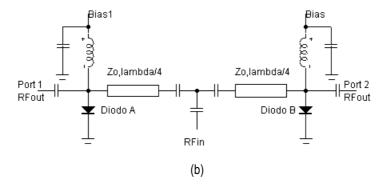

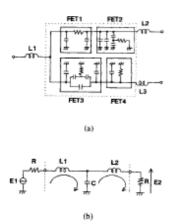

# 3.3.2. <u>Conmutadores SPDT MMIC para DC-40 GHz y 20-40</u> GHz

Aquí nos basamos en el artículo titulado "DC-40 GHz and 20-40 GHz MMIC SPDT Switches" ([6]). Nos muestran el diseño y fabricación de dos switches de banda ancha, en tecnología MMIC y que usan transistores FET's de longitud de puerta de 0.35 μm.

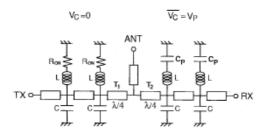

En la figura 3.6 se muestra la topología del switch SPDT de 20-40 GHz.

Figura 3.6