#### 6. Adaptación del DSP.

El control de todo el sistema se realizará desde la placa eZdsp<sup>TM</sup>F2812 de Texas Instruments, la cual dispone de un DSP TMS320F2812, el cual tiene doce canales PWM, pero los cuales se obtienen a partir de seis comparadores, siendo seis de los canales dependientes de los otros seis. Como necesitamos ocho señales PWM independientes, habrá que introducir entre la placa del DSP y el convertidor unos circuitos lógicos secuenciales para conseguir los disparos tal y como los queremos. Estos circuitos los implementaremos mediante dispositivos PAL. Una PAL se utilizará simplemente como contador, ya que se necesitará uno para implementar los tiempos muertos en los disparos de los IGBT's, al no poder utilizar directamente los canales del DSP. Otras dos PAL's se usarán para los disparos de cada una de las ramas del convertidor.

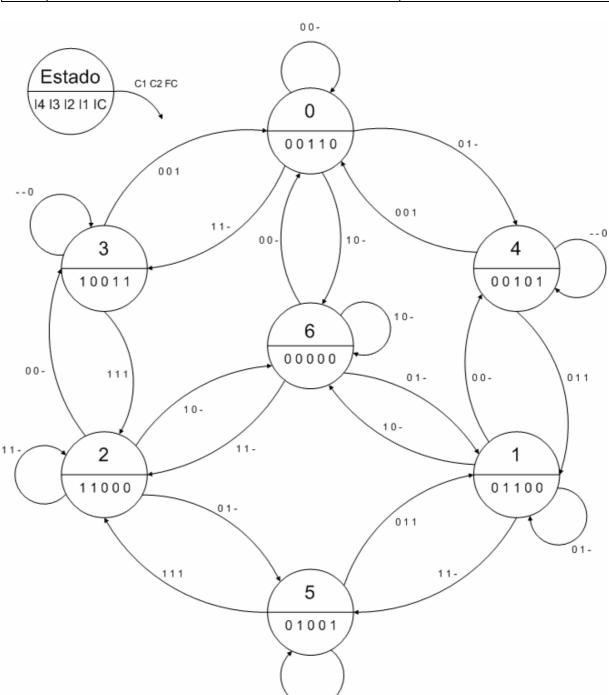

Por ser sistemas lógicos secuenciales se regirán por una máquina de estados mediante la cual se determinarán las salidas que irán hacia los drivers de los IGBT's. Para cada una de las ramas tenemos tres estados posibles de funcionamiento, con otros tantos estados intermedios posibles a los que hay que añadir un estado adicional de reposo, la máquina de estados de cada una de las ramas se muestra en la Figura 30. En cada una de las PAL's en las que se implementarán los disparos se necesitarán ocho salidas, cuatro para los IGBT's de cada rama, tres para configurarlas como biestables para el número de estados que tenemos y la última para indicar a la PAL del contador que tiene que comenzar la cuenta.

Figura 30. Máquina de estados de la PAL de los disparos.

|   | Proyecto Fin de Carrera                              | Alumno                         |

|---|------------------------------------------------------|--------------------------------|

|   | Diseño e implementación de un convertidor monofásico | José Francisco Campos Bizcocho |

| 5 | de cinco niveles con control basado en DSP           |                                |

#### 6.1. Tablas de estados y de Karnaugh.

| Entr.: FC C1 C2  | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 | IGBT1 | IGBT2 | IGBT3 | IGBT4 | IC |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|----|

| 0 (Nivel bajo)   | 0   | 4   | 6   | 3   | 0   | 4   | 6   | 3   | 0     | 0     | 1     | 1     | 0  |

| 1 (Nivel medio)  | 4   | 1   | 6   | 5   | 4   | 1   | 6   | 5   | 1     | 0     | 0     | 1     | 0  |

| 2 (Nivel alto)   | 3   | 5   | 6   | 2   | 3   | 5   | 6   | 2   | 1     | 1     | 0     | 0     | 0  |

| 3 (Nivel int. 1) | 3   | -   | -   | 3   | 0   | -   | -   | 2   | 0     | 1     | 1     | 0     | 1  |

| 4 (Nivel int. 2) | 4   | 4   | -   | -   | 0   | 1   | -   | 1   | 1     | 0     | 1     | 1     | 1  |

| 5 (Nivel int. 3) | -   | 5   | -   | 5   | -   | 1   | -   | 2   | 1     | 1     | 0     | 1     | 1  |

| 6 (Reposo)       | 0   | 1   | 6   | 2   | 0   | 1   | 6   | 2   | 0     | 0     | 0     | 0     | 0  |

Tabla 4. Tabla de estados de la PAL de disparos.

La tabla de estados representada tiene los siete estados posibles de una rama del convertidor, los tres niveles de conexión normal, los tres niveles intermedios para pasar entre niveles y el estado de reposo. Las entradas necesarias para conocer el estado siguiente al que pasar son las señales de los dos comparadores de una rama y la señal de fin de cuenta del tiempo muerto que dará la PAL del contador. Las columnas de la derecha muestran las salidas de los estados, las cuales son las señales de puerta para los IGBT's y la señal de iniciar la cuenta del tiempo muerto. En la tabla las señales de los IGBT's son negadas, puesto que el driver usado niega la entrada, de esta forma tenemos que darle la señal negada a la entrada para que a la salida tengamos la señal necesaria para activar el dispositivo.

A partir de la tabla de estados, obtendremos las tablas de Karnaugh para los biestables que representarán el estado en el que nos encontremos. Puesto que tenemos siete estados posibles, necesitaremos tres biestables para poder representarlo. Una vez obtenida la tabla de Karnaugh para cada biestable, se obtendrán la ecuación lógica que dará la señal de salida de cada biestable. En nuestro caso, al tener seis variables (tres biestables y tres entradas), la tabla de Karnaugh será tridimensional con dos variables por lado. Para su representación en este documento se pondrán las cuatro tablas de dos variables en cada lado que formarían el cubo, indicando en la parte superior de cada una de las tablas el valor de las dos variables que le pertenecen a la tercera dimensión.

José Francisco Campos Bizcocho

### • **Q0**:

$\overline{C1} \cdot \overline{C2}$

| Q0 FC<br>Q2Q1 | 00 | 01 | 11 | 10 |

|---------------|----|----|----|----|

| 00            | 0  | 0  | 0  | 0  |

| 01            | 1  | 1  | 0  | 1  |

| 11            | 0  | 0  | -  | -  |

| 10            | 0  | 0  | ı  | ı  |

$\overline{C1} \cdot C2$

| Q0 FC |    |    |    |    |

|-------|----|----|----|----|

| Q2Q1  | 00 | 01 | 11 | 10 |

| 00    | 0  | 0  | 1  | 1  |

| 01    | 1  | 1  | -  | -  |

| 11    | 1  | 1  | -  | -  |

| 10    | 0  | 1  | 1  | 1  |

$C1 \cdot C2$

| Q0 FC<br>Q2Q1 | 00 | 01 | 11 | 10 |

|---------------|----|----|----|----|

| 00            | 1  | 1  | 1  | 1  |

| 01            | 0  | 0  | 0  | 1  |

| 11            | 0  | 0  | -  | -  |

| 10            | -  | -  | 0  | 1  |

$C1\cdot\overline{C2}$

| Q0 FC<br>Q2Q1 | 00 | 01 | 11 | 10 |

|---------------|----|----|----|----|

| 00            | ı  | ı  | ı  | 1  |

| 01            | ı  | ı  | ı  |    |

| 11            | 0  | 0  | -  | -  |

| 10            | -  | -  | -  | -  |

$$\begin{aligned} \mathbf{Q0} &= \mathbf{Q0} \cdot \overline{\mathbf{C1}} \cdot \mathbf{C2} + \mathbf{Q1} \cdot \overline{\mathbf{Q0}} \cdot \overline{\mathbf{C1}} \cdot \mathbf{C2} + \mathbf{Q2} \cdot FC \cdot \overline{\mathbf{C1}} \cdot \mathbf{C2} + \mathbf{Q0} \cdot \overline{FC} \cdot \mathbf{C2} + \overline{\mathbf{Q2}} \cdot \mathbf{Q1} \cdot \overline{FC} \cdot \overline{\mathbf{C1}} + \\ &+ \overline{\mathbf{Q2}} \cdot \overline{\mathbf{Q1}} \cdot \mathbf{C1} \cdot \mathbf{C2} + \overline{\mathbf{Q2}} \cdot \mathbf{Q1} \cdot \overline{\mathbf{Q0}} \cdot \overline{\mathbf{C1}} \end{aligned}$$

Tabla 5. Tablas de Karnaugh y ecuación lógica para Q0.

|   | Proyecto Fin de Carrera                              | Alumno                         |

|---|------------------------------------------------------|--------------------------------|

|   | Diseño e implementación de un convertidor monofásico | José Francisco Campos Bizcocho |

| 5 | de cinco niveles con control basado en DSP           | -                              |

# • <u>Q1:</u>

| $C1\cdot C2$  |    |    |    |    |  |  |  |

|---------------|----|----|----|----|--|--|--|

| Q0 FC<br>Q2Q1 | 00 | 01 | 11 | 10 |  |  |  |

| 00            | 0  | 0  | 0  | 0  |  |  |  |

| 01            | 1  | 1  | 0  | 1  |  |  |  |

| 11            | 0  | 0  | -  | -  |  |  |  |

| 10            | 0  | 0  | -  | -  |  |  |  |

| <i>C</i> 1· <i>C</i> 2 |    |    |    |    |  |  |  |

|------------------------|----|----|----|----|--|--|--|

| Q0 FC<br>Q2Q1          | 00 | 01 | 11 | 10 |  |  |  |

| 00                     | 0  | 0  | 0  | 0  |  |  |  |

| 01                     | 0  | 0  | -  | 1  |  |  |  |

| 11                     | 0  | 0  | -  | -  |  |  |  |

| 10                     | 0  | 0  | 0  | 0  |  |  |  |

$C1 \cdot \overline{C2}$

$Q1 = C1 \cdot \overline{C2} + \overline{Q0} \cdot C1 + Q1 \cdot C1 + Q2 \cdot FC \cdot C1 + \overline{Q2} \cdot Q1 \cdot \overline{Q0} \cdot \overline{C2} + Q1 \cdot Q0 \cdot \overline{FC}$

Tabla 6. Tablas de Karnaugh y ecuación lógica para Q1.

### • Q2:

|               | $\overline{C1}\cdot\overline{C2}$ |    |    |    |  |  |  |  |

|---------------|-----------------------------------|----|----|----|--|--|--|--|

| Q0 FC<br>Q2Q1 | 00                                | 01 | 11 | 10 |  |  |  |  |

| 00            | 0                                 | 0  | 1  | 1  |  |  |  |  |

| 01            | 0                                 | 0  | 0  | 0  |  |  |  |  |

| 11            | 0                                 | 0  | -  | -  |  |  |  |  |

| 10            | 1                                 | 0  | ı  | -  |  |  |  |  |

| $C1\cdot C2$  |    |    |    |    |  |  |  |

|---------------|----|----|----|----|--|--|--|

| Q0 FC<br>Q2Q1 | 00 | 01 | 11 | 10 |  |  |  |

| 00            | 1  | 1  | 0  | 0  |  |  |  |

| 01            | 1  | 1  | -  | -  |  |  |  |

| 11            | 0  | 0  | -  | -  |  |  |  |

| 10            | 1  | 0  | 0  | 1  |  |  |  |

Q0 FC 00 01 11 10 Q2Q1 00 0 0 1 1 01 0 0 0 0 11 0 0 10 0 1

$C1 \cdot C2$

$C1 \cdot \overline{C2}$

$$Q2 = C1 \cdot \overline{C2} + Q2 \cdot \overline{Q1} \cdot \overline{FC} + Q2 \cdot \overline{Q0} \cdot \overline{C1} \cdot C2 + \overline{Q1} \cdot Q0 \cdot \overline{C2} + \overline{Q2} \cdot \overline{Q1} \cdot Q0 \cdot C1$$

Tabla 7. Tablas de Karnaugh y ecuación lógica para Q2.

Para completar la programación de la PAL de los disparos hay que indicar las ecuaciones que regirán las salidas. Para cada una de las salidas se realizará una tabla de Karnaugh para poder obtener la ecuación.

#### IGBT1:

| Q1Q0<br>Q2 | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 0          | 0  | 1  | 0  | 1  |

| 1          | 1  | 1  | -  | 1  |

$$I1 = Q2 + \overline{Q1} \cdot Q0 + Q1 \cdot \overline{Q0}$$

Tabla 8. Tabla y ecuación para el IGBT1.

#### • *IGBT2:*

| Q1Q0<br>Q2 | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 0          | 0  | 0  | 1  | 1  |

| 1          | 0  | 1  | -  | 1  |

$$I2 = Q1 + Q2 \cdot Q0$$

Tabla 9. Tabla y ecuación para el IGBT2.

#### • *IGBT3*:

| Q1Q0<br>Q2 | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 0          | 1  | 0  | 1  | 0  |

| 1          | 1  | 0  | -  | 1  |

$$I3 = \overline{Q1} \cdot \overline{Q0} + Q1 \cdot Q0 + Q2 \cdot \overline{Q0}$$

Tabla 10. Tabla y ecuación para el IGBT3.

### • <u>IGBT4:</u>

| Q1Q0<br>Q2 | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 0          | 1  | 1  | 0  | 0  |

| 1          | 1  | 1  | -  | 1  |

$$I4 = \overline{Q1} + Q2$$

Tabla 11. Tabla y ecuación para el IGBT4.

## • <u>IC:</u>

| Q1Q0<br>Q2 | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 0          | 0  | 0  | 1  | 0  |

| 1          | 1  | 1  | -  | 0  |

$$IC = Q2 \cdot \overline{Q1} + Q1 \cdot Q0$$

Tabla 12. Tabla y ecuación para IC.

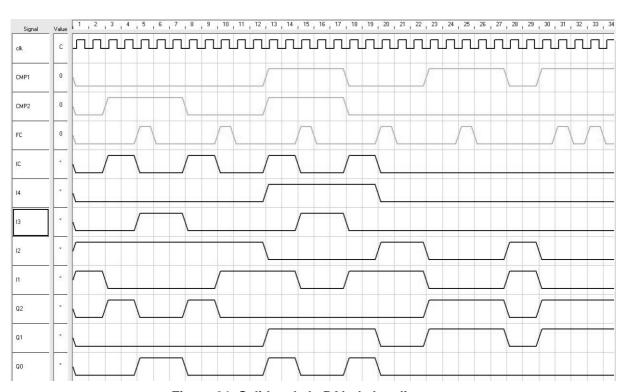

Mediante el programa WinCupl 5.30.2 se realizan las simulaciones de funcionamiento de los programas de las PAL's. En este programa hay que indicar los pines que actuarán como entradas y los que actuarán como salidas, poniendo después las ecuaciones que regirán los valores de las salidas dependiendo del estado en que se encuentre el sistema y las entradas que haya en ese momento. En la Figura 31 se muestra la simulación de la PAL de los disparos, las señales de entrada son CMP1 y CMP2 provenientes de los comparadores, la señal FC que proviene de la PAL del contador e indica el final de la cuenta del tiempo muerto necesario para los IGBT's y la señal del reloj, CLK. En la simulación se han puesto varias combinaciones de entradas para poder observar los cambios que se pueden dar en las mismas. Además la señal de fin de cuenta del tiempo muerto se da después de dos ciclos después del cambio de entradas, para no hacer excesivamente larga la simulación.

Figura 31. Salidas de la PAL de los disparos.

|   | Proyecto Fin de Carrera                              | Alumno                         |

|---|------------------------------------------------------|--------------------------------|

|   | Diseño e implementación de un convertidor monofásico | José Francisco Campos Bizcocho |

| 5 | de cinco niveles con control basado en DSP           | -                              |

La PAL del contador tendrá ocho salidas ocupadas para los biestables de dicho contador, con lo que se podrá contar hasta 2<sup>8</sup> ciclos de reloj, como ya se explicó anteriormente. De las salidas que quedan libres, una será la que utilizaremos para indicar a la PAL de los disparos que ha finalizado la cuenta del tiempo muerto. No se usan las diez salidas porque la ecuación que correspondería al noveno bit del contador tiene demasiados términos para programarlos en la PAL.

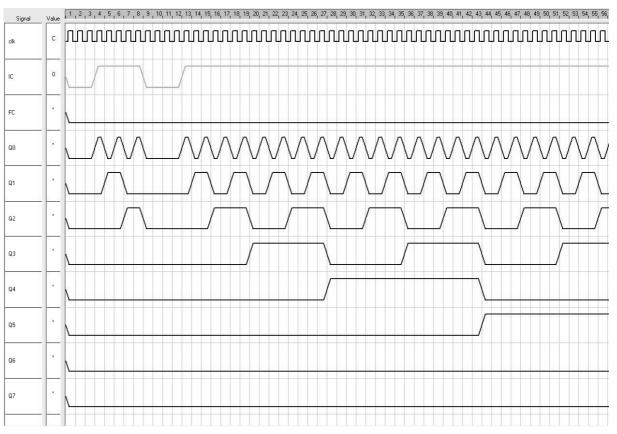

Podemos observar en la Figura 32 y en la Figura 33 las simulaciones realizadas para el caso de la PAL del contador, en la primera figura se puede ver que la cuenta se inicia desde cero cada vez que se activa la señal de salida de la PAL de los disparos (IC) y, en la segunda, podemos ver como se activa la señal de fin de cuenta (FC) cuando se alcanza el valor que hace ponerse a uno el bit séptimo del contador. Además se puede ver también que al poner la señal IC a cero, la señal FC también se pone a cero de nuevo.

Figura 32. Simulación del comienzo de cuenta del contador.

Figura 33. Simulación del fin de cuenta del contador.

La programación del contador se ha realizado mediante máquinas de estado, de forma que cada paso del contador es un estado diferente, necesitando para pasar al siguiente estado que se dé un flanco de subida de reloj, con lo que habrá que tener en cuenta que el contador diseñado dividirá por dos la frecuencia de entrada de reloj para saber la equivalencia del número de ciclos con el tiempo muerto que necesitemos.

#### 6.2. Señales de la placa del DSP.

Desde el DSP tendremos que llevar primeramente la señal de reloj, el cual tiene una frecuencia de 150MHz, aunque la señal que tomaremos será XCLKOUT, la cual puede configurarse para ser una cuarta parte de la original, de forma que tendremos una señal de reloj para las PAL's de 37'5MHz.

El resto de señales que tomaremos desde el DSP serán las de los módulos PWM del mismo, usando las señales correspondientes a PWM1, PWM3, PWM8 y PWM10, dos para una PAL de disparos y otras dos para la otra.

| Ī |   | Proyecto Fin de Carrera                              | Alumno                         |

|---|---|------------------------------------------------------|--------------------------------|

|   |   | Diseño e implementación de un convertidor monofásico | José Francisco Campos Bizcocho |

|   | 5 | de cinco niveles con control basado en DSP           |                                |

Las medidas que realizamos en la placa del convertidor se pasan hacia los convertidores Analógico-digitales del DSP. Para poder muestrear simultáneamente las corrientes y tensiones de los condensadores, se usan los siguientes canales de dichos convertidores.

- VDC1: ADCINB2, que corresponde al PIN 3 del puerto P5 del DSK.

- VDC2: ADCINA2, que corresponde al PIN 6 del puerto P9 del DSK.

- VAC: ADCINB4, que corresponde al PIN 5 del puerto P5 del DSK.

- IDC1: ADCINB3, que corresponde al PIN 4 del puerto P5 del DSK.

- IDC2: ADCINA3, que corresponde al PIN 8 del puerto P9 del DSK.